jeffrey.kissel@LIGO.ORG - posted 14:12, Wednesday 19 April 2017 - last comment - 16:44, Wednesday 19 April 2017(35668)

Tried Repeating SRC Detuning Manipulation Study, Failed.

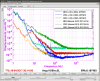

J. Kissel I attempted to repeat Evan Hall's study (LHO aLOG 27675) in which he was able to manipulate the detuning of the DARM response with a SRCL offset, but was unsuccessful. (1) I was able only to inject an offset of +/-100 [ct] in H1:LSC-SRCL1_OFFSET and have the IFO stable (I tried offsets of +/-200 like Evan had done, and then +/-150, but both cause a lock-loss) (2) With a +/-100 [ct] SRCL offset, the new SRC detuning parameter tracking did not show any signs of spring frequency change. Offset ramping times were 120 [sec]. When at +/-150 [ct], there was visible excess noise in SRCL, which then propagated through standard coupling to DARM (see attachement for comparison between no offset and -150 ct gathered just before lock loss). I did not have time to take sweeps as Evan did. Recall that at Evan's study was done at with an O1, 10 W IFO. Perhaps the calibration of the offset (he suggests 0.1 [ct/pm]) changes with input power; he doesn't give enough detail about his SRCL budget to re-derive the calibration. Will look into the theory more before attempting this again. It's discouraging that, although the SRC detuning frequency calculation from 7.93 Hz PCALY line appears roughly correct compared to recent sensing function sweeps, the calculation appears to be insensitive to this known thing that manipulates it. #backtothedrawingboard

Images attached to this report

Comments related to this report

J. Kissel, K. Izumi

Izumi-sensei has come to my rescue. He imparts the following knowledge:

(1) The SRCL calibration is independent of input power, and the same at DC as it is at AC because the optical plant is flat for SRCL.

(2) That calibration is stored in the CAL-CS model (specifically the H1:CAL-CS_SUM_SRCL_ERR filter bank, FM1), calibrating the very channels I'd posted in the spectra above:

-9.55e-6 [um/ct] = 9.55e-12 [m/ct] ~= 10 [pm/ct] == >> 0.1 [ct/pm]

i.e. the number that Evan quotes in LHO aLOG 27675 which comes from Kiwamu's original model of the SRCL open loop gain (LHO aLOG 18742)

(3) The proof is in the pudding: we don't scale the SRCL gain at all during a normal lock acquisition sequence when we increase from 10 to 30 W.

In summary, there's no obvious reason why the OFFSET calibration should have changed between Evan's measurement and my own today. And to repeat what was said above -- there was no evidence of change in the live calculation of the SRC detuning spring frequency.

Something is rotten in the state of Denmark...