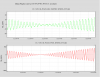

Yesterday I modified the end station cal models to add the FPGA duotone signal to the commissioning frame. When analysing the data, I noticed that the non-filtered loop back duotone signal has a low amplitude. In the attachment below, the red plot is the FPGA duotone signal zoomed at the zero crossing point. This signal has a maximum amplitude of 4000 counts over the whole second. The green plot is the IOP loop-backed duotone, again zoomed in. This plot has a max amplitude of 250 counts, so at the zero crossing the bit noise is apparent. The reduction of the amplitude is due to the difference in the voltage range and bit range of the DAC compared to the ADC (ADC is 16bit, +/- 20V, DAC is 18bit +/- 10V). There is a missing factor of 2, perhaps the differential signal is converted to single ended in the loop-back circuit?

Rick thinks we dont need to do anything for O1 to boost the non-filt amplitude. One solution would be to use additional DAC and ADC channel and perform the loop-back external to the IO Chassis, sending the signal out through a gain to compensate for the amplitude loss.