In addition to what are already in integration issue tracker (https://services.ligo-la.caltech.edu/FRS/show_bug.cgi?id=6500), the following changes need to be done. Both are in T0900577.

ilspmc_servo3.pdf (both for PMC and ILS):

After the demod, 5MHz corner of Sallen-Key is unnecessarily high, and AD797 open loop gain is about 12dB or so at 5MHz, so it's not like it works as intended.

We'll add a passive 5MHz pole, and move the Sallen-Key corner down to 170kHz or so by:

- 470pF in parallel with R81

- Change C3 to 6.8nF

- Change C34 to 820pF

ilspmc_fieldbox4.pdf (both for PMC and ILS):

The DAC output for ramp signal is permanently connected to the HV amp with 200Hz pole and a factor of 50 gain.

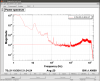

If DAC output noise is 1uV/sqHz (depends on the DAC output but the digital output is usually zero), the DAC noise in the HV monitor (which has a 1/50 attenuation) will be 1uV/sqHz at DC and it goes down above 200Hz. See attached for the PMC HV monitor signal in-lock.

We'll add zp=100:10 by stuffing the unused whitening pattern on the board:

- Remove J1

- N4 OP27

- R7 140k

- R8 15.4k

- R9 140k

- C2 100nF

These are added to the existing FRS, which already has similar modifications to HV monitor and mixer readback.

Note that only the HV mon modification for PMC board was done, and we intend to do the rest for PMC as well as ILS.