During one of our powerups today, I measured the PRCL gain several (52) times. The goal is to see if we really need the big lookup table of nested IF statements in the increase power guardian states that currently changes the PRCL digital gain (or even more complicated, a UGF servo), or can we simplify the PRCL gain setting as we power up.

The problem is that the UGF drops as the interferometer thermalizes at higher powers. The nested IF statements are trying to keep the PRCL UGF always roughly constant. But, the phase bubble of the PRCL loop is pretty generous, so we can handle a fair amount of gain drift. The edges of the phase bubble are at 13 degrees and 121 degrees, so as long as we don't get close to either of those values, we should be fine.

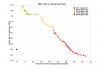

Attached is the PRCL UGF plotted versus time since my first measurement at 2W. The colors of the dots indicate what PSL injected power we were using at that time, as labeled in the legend. The legend also shows what digital gain was in the PRCL servo at that time. At 2W it is half the value of the higher power values. But, note that all the 20W+ measurements have a constant digital gain, while the UGF is dropping by about a factor of 2. The highest UGF when we first arrive at 20W is 84 Hz, with a phase margin of 23 degrees. The lowest UGF here is 39 Hz with a phase margin of 35 degrees.

The peak of the phase bubble is at about 45 Hz, so that's where we want the UGF to end up when we're done. Right now, the state LOWNOISE_LENGTH_CONTROL sets the digital gain down to 11 from 16, so I think it probably has been setting the final nominal low noise PRCL UGF to be 27 Hz, which has a phase margin of about 28 degrees. This value of 11 for the digital gain was set in Oct 2018, when we were using 20W PSL power. So, with the new 30W of PSL power, I am changing the value in the guardian to be 16, where all of my measurements are.

My conclusion here is that we can go to 20W, set the PRCL gain to be 16 (which puts the UGF at the high side of the phase bubble), and then just leave it and it will relax to a final of 38 or 39 Hz. Then, in LownoiseLengthControl we can set the gain to be a bit higher to bump the UGF back to 45Hz. Anyone is welcome to do this, and remove the nested IF statementss from the powerup states, and put the higher value into LownoiseLengthControl, but I don't want to do something so big minutes before I walk out the door.....

T Vo, Sheila

On the next lock acquisition we edited the POWER_30W state to remove the changes in PRCL digital gain, it is set to 16 in LOW_NOISE_LENGTH_CONTROL. This seems OK.