louis.dartez@LIGO.ORG - posted 16:50, Friday 24 January 2025 - last comment - 13:25, Monday 27 January 2025(82446)

AA filter engaged in DCPD path, and calibration updated

Today we re-engaged the 16k Digital AA Filter in the A and B DCPD paths then re-updated the calibration on the front end and in the gstlal-calibration (GDS) pipeline before returning to Observing mode. ### IFO Changes ### * We engaged FM10 in H1OMC-DCPD_A0 and H1OMC-DCPD_B0 (omc_dcpd_filterbanks.png). We used the command in LHO:82440 to engage the filters and step the OMC Lock demod phase (H1:OMC-LSC_PHASEROT) from 56 to -21 degrees (77 degree change). The 77 degrees shift is necessary to compensate for the fact that the additional 16k AA filter in the DCPD path introduces a 77 degree phase shift at 4190Hz (the oscillator frequency at which the dither line that the OMC Lock servo is locked to) (omc_lock_servo.png). All of these changes (the FM10 toggles and the new OMC demod phase value) have been saved in the OBSERVE and SAFE sdfs. * It was noted in the control room that the range was quite low (153Mpc) and re remembered that we might want to tune the squeezer again as Camilla had done yesterday (LHO:82421). We have not done this. * Preliminary analysis of data taken with this newly installed 16k AA filter engaged suggests that the filter is helping (LHO:82420). ### Calibration Changes ### We pushed a new calibration to the front end and the GDS pipeline based on the measurements in 20250123T211118Z. In brief, here are a few things we learned/did: - The inverse optical gain (1/Hc) filter changes are not being exported to the front endat all . This is a bug. - We included the following delays in the actuation path: uim_delay = 23.03e-6 [s] pum_delay = 0 [s] tst_delay = 20.21e-6 [s] These values are stored in the pydarm_H1.ini file. - The pyDARM parameter set also contains a value of 198.664 for tst_drive_align_gain, which is inline with CALCS (H1:CAL-CS_DARM_FE_ETMX_L3_DRIVEALIGN_L2L_GAIN) and the ETMX path in-loop (H1:SUS-ETMX_L3_DRIVEALIGN_L2L_GAIN). - There is still a 5% error at 30Hz that is not fully understood yet. Broadband pcal2darm comparison plots will be posted in a comment.

Images attached to this report

Comments related to this report

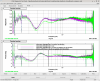

I'm attaching a PCALY2DARM comparison to show where the calibration is now compared against what it was before the cal-related work started. At present (dark blue) we have a 5% error magnitude near 30Hz and roughly a 2degree maximum error in phase. The pink trace shows a broadband of PCALY to GDS-CALIB_STRAIN on Saturday, 1/25. This is roughly 24hrs after the cal work was done and I plotted it to show that the calibration seems to be holding steady. The bright green trace is the same measurement taken on 1/18, which is before the recent work to integrate the additional 16k AA filter in the DCPD path began. All in all, we've now updated the calibration to compensate for the new 16k AA filter and have left the calibration better than it was when we found it. More discussion related to the cause of the large error near 30Hz is to come.

Images attached to this comment