jeffrey.kissel@LIGO.ORG - posted 10:53, Wednesday 21 May 2025 - last comment - 10:56, Wednesday 21 May 2025(84509)

Gain of 4x added to COILOUTFs for OSEM Stages in h1susb123 that got a 20-bit DAC upgrade this Morning

J. Kissel, R. Short

Given that h1susb123 had an emergency upgrade to 20-bit DACs this morning, we need to do "the usual" cheat to ensure the upstream loops that use the stages that got upgrade don't notice a difference -- add a "20bitDAC" gain of 4.0x to the COILOUTF banks in FM10 of any stage that got the upgrade from 18- to 20-bit DACs. This accounts for the change in calibration from 20V / 2^18 to 20V / 2^20.

This has been done for the

- H1 SUS ITMY M0 F1F2F3SD

- H1 SUS ITMY R0 F1F2F3SD

- H1 SUS ITMY M0 LFRT / R0 LFRT

- H1 SUS ITMY L1 ULLLURLR

- H1 SUS ITMX M0 F1F2F3SD

- H1 SUS ITMX R0 F1F2F3SD

- H1 SUS ITMX M0 LFRT / R0 LFRT

- H1 SUS ITMX L1 ULLLURLR

- H1 SUS BS M1 F1F2F3LF

- H1 SUS BS M1 RTSDxxx

COILOUTF banks, corresponding to all the stages that got upgraded this morning.

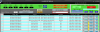

Attached are the automatically generated "diff" screens for each model showing that I added the gain(4) design string in each 9th module (counting starting a 0, that's FM10) to all of the above mentioned OSEMs.

I then hit "LOAD_COEFFICIENTS" on each user model's GDS_TP screen (which clears the diff).

The filter file changes have been committed to

/opt/rtcds/userapps/release/sus/h1/filterfiles

H1SUSBS.txt

H1SUSITMX.txt

H1SUSITMY.txt

as of rev 31491.

Ryan accepted FM10 being ON for all of the above mentioned OSEM chains in the

h1susitmy_down.snap

h1susbs_down.snap

h1susitmx_down.snap

and

h1susitmy_observe.snap

h1susitmx_observe.snap

h1susbs_observe.snap

as of rev 31492.

Images attached to this report