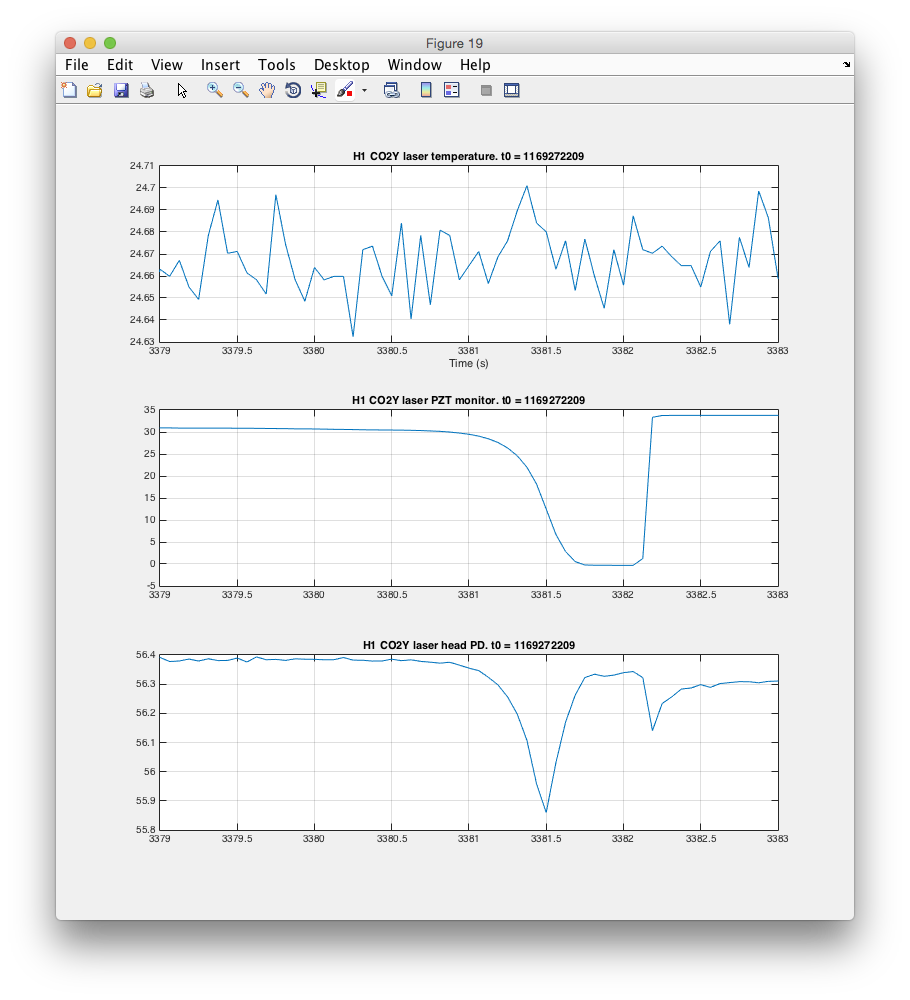

Detchar noticed glitches in h(t) due to snow plowing on Jan 13. LHO alog entries noting ongoing plowing were extremely helpful for figuring out what these glitches were. See the first attachment for spectrograms of an example snow plow glitch showing that near a VEA the initial impact of the plow on the ground and the subsequent scraping of the ground couples into h(t) up to ~100 Hz (witnessed by the ground STS2s, HEPI L4Cs and ISI GS13s). The last spectrogram shows the clear cadence of the plowing near the corner station on an 8 minute timescale.

Building on a DQ flag Laura added to identify when snow plowing was happening near a VEA on Jan 09-10 (alog 33116), I looked at the BLRMS (10-30, 3-10, and 1-3 Hz) for a couple weeks after that day to suggest other times to flag.

The second attachment shows BNS range and the 10-30 Hz BLRMS for days of interest. I used times noted in the alogs as when snow plowing was happening (marked in blue and orange) as a baseline to identify other potential snow plow times not mentioned in the alogs (marked in red).

Seismic glitches identified on Jan 19 and 20 (marked in purple) are likely unrelated to plowing and should be caught with an automated 10-30 Hz or 3-10 Hz BLRMS threshold DQ flag.

I recommend all identified times (blue, orange, and red) from Jan 09-20 be flagged with H1:DCH-SNOW_PLOW (v2).

-

Jan 09 2017 13:00-15:22 UTC

-

[Jan 09-10 2017 segment already flagged by DCH:SNOW_PLOW v1: 1168040718-1168046718]

-

Jan 10 2017 23:00-23:45 UTC

-

Jan 11 2017 19:45-20:05 UTC

-

Jan 11 2017 21:45-22:10 UTC

-

Jan 12 2017 00:00-00:50 UTC

-

Jan 13 2017 14:30-16:15 UTC

-

Jan 13 2017 17:00-18:30 UTC

-

Jan 17 2017 15:30-16:35 UTC

-

Jan 20 2017 02:00-03:00 UTC

-

Jan 20 2017 12:30-13:00 UTC