TITLE: 10/27 Day Shift: 15:00-23:00 UTC (08:00-16:00 PST), all times posted in UTC

STATE of H1: Commissioning

INCOMING OPERATOR: TJ

SHIFT SUMMARY: Locked at NLN for the first couple hours of my shift. Robert doing PEM injections during this period until lock was broken due to me forgetting to turn off the BRS and Robert getting too close to it. Middle part of the day was Betsy cleaning the PSL viewport. Then we immediately had another EQ when they finished. Relocking commenced in the last couple of hours of my shift.

LOG:

15:00 Robert to LVEA doing PEM injections. Took IFO out of Observing mode due to the injections.

16:40 Robert to EY for PEM inj.

17:45 Betsy, Robert, Peter, Richard to LVEA

17:50 Peter out

17:52 Chandra to MY

19:00 Fil to LVEA

19:08 Fil out

19:30 Fil to LVEA

20:02 Richard to LVEA

20:50 Betsy, Robert done

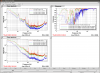

Note: The dust monitor PSL 102 has been alarming on and off all day. See attached screenshot for the trend for today. The thresholds are 70 for minor alarm and 100 for major for both particle sizes.