POP_A_RF9_I to SRCL matrix element is no -0.025. This cleaned up at least the SRCL error point a little. THe change is in the guardian.

POP_A_RF9_I to SRCL matrix element is no -0.025. This cleaned up at least the SRCL error point a little. THe change is in the guardian.

We've been locked at 26 Watts looking at low frequency noise, so just to make things easier I cut the HARD pit loops off a little bit lower.

I lowered the gain of DHARD P from 30 to 20, I lowered CHARD P from -0.15 to -0.14. I replaces the JLP25 filters with second order elipticals at 10 Hz. I put this in the guardian to happen when we are locked below 45 Watts.

This helps DARM from about 15-27 Hz. In the attached screenshot you can see how DARM and the coherences changed.

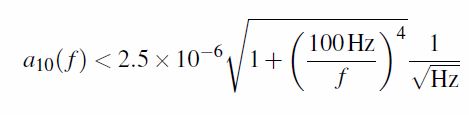

In the past few weeks and months it has been becoming increasingly clear that we are limited by beam jitter when going to higher power. The beam jitter requirements were derived assuming an rms misalignment of the test masses of 10-9 rad rms in units of divergence angle or beam radius; see T0900142. The coupling mechanism is through the symmetric alignment matrix which mixes TEM00 and TEM10 modes. This transforms jitter in the first order mode back to zeroth order where it beats against the carrier field to produce an intensity fluctuation. This mechanism is independent of the OMC, since the intensity noise is generated in the interferometer. The jitter requirement into the input mode cleaner is:

We can compare this with the measurement from alog 30237 in the attached pdf. The solid olive curve represents the requirement which is a factor of 10 below the level (dashed olive line) one would expect the noise to be visible in the gravitational wave readout at full power and assuming a 10-9 rms misalignment.

The following observations can be made:

Possible alternative explanations to the visible HPO jitter in the gravitational wave readout at 50 W input:

16:44 Begin bringing back IFO from computer crash.

17:06 Begin aligning/locking process

17:48 on the hone with Dave Barker about a ALS_XARM guardian node I was having trouble restarting. Ezca connection error to H1:ALS-X_WFS_SWITCH channel

22:00 Damping ITMY bounce mode. Flipped sign on gain and added .1 gain

22:40 damped PI mode 27 by flipping the sign and then adding 30 degrees to the phase.

22:58 PI Mode 27 needed another sign flip

22:47 NLN ≈60MPc. Handing off to Nutsinee

BruCo report for last night lock can be found here:

https://ldas-jobs.ligo.caltech.edu/~gabriele.vajente/bruco_1161255617/

Ed, Sheila

Trouble with LOCKING_ALS sent us looking for HV settings on ETMX. It seemed that the L3 stages were set to LO volts rather than HI. We believe what happened when we toggled the L3 LL HI/LO control that the state of the UL changed as well. We're also not sure why SDF didn't grab this change and we couldn't find it in SDF with a search.

A similar thing:

OMCDCPD whitening settings were incorrect and the DCPD_MATRIX elements were all zero. these record did exist in SDF, but were set to zero in SDF.

This morning started with a smorgasboard of troubles. Patrick aLogged what happened there. After we seemingly got everything back up there were still some lingering issues with connections/channels that were finally resolved through a half-dozen or so phone calls with Dave Barker. His aLogs should show the gory details. I'm finally tying to get things re-aligned so I can get this ship sailing again.

Existing MEDMs continued to be connected to h1iscex, but no new connections were possible. Also I was unable to ping or ssh to h1iscex on the FE-LAN. This also meant that the Dolphin manager was unable to put this node into an offline state. The only recourse was to put SUS-EX and SEI-EX into a safe state and remotely power cycle h1iscex via its IPMI management port. As expected, this in turn glitched the attached Dolphin nodes in the EX-Fabric (h1susex and h1seiex). I restarted all the models on these two systems and Ed is now recovering EX.

at approximately 07:50 PDT this morning the /opt/rtcds file system (served by h1fs0) became full. This caused some front end epics processes to segfault (example dmesg output for h1susb123 shown below). Presumably these models epics processes were trying to do some file access at this time. The CDS overview is attached showing which specific models had problems. At this point guardian stopped running because it could not connect to critical frontends. Lockloss_shutter_check also reported an NDS error at this time (log shown below), further investigation is warrented since h1nds0 was running at the time.

On trying to restart h1susitmx, the errors showed that /opt/rtcds was full. This is a ZFS file system, served by h1fs0. I first attempted to delete some old target_archive directories, but ran into file-system-full errors when running the 'rm' command. As root, I manually destroyed all the ZFS Snapshots for the month of May 2016. This freed up 22.3GB of disk which permitted me to start the failed models.

Note that only the model EPICS processes had failed, the front end cores were still running. However in order to cleanly restart the models I first issued a 'killh1modelname' and then ran 'starth1modelname'. Restarting h1psliss did not trip any shutters and the PSL was operational at all times.

I've handed the front ends over to Patrick and Ed for IFO locking, I'll work on file system cleanup in the background.

I've opened FRS6488 to prevent a re-occurance of this

[1989275.036661] h1susitmxepics[25707]: segfault at 0 ip 00007fd13403c894 sp 00007fffb426b9a0 error 4 in libc-2.10.1.so[7fd133fda000+14c000]

[1989275.045095] h1susitmxepics used greatest stack depth: 2984 bytes left

[1989275.086076] h1susbsepics[25384]: segfault at 0 ip 00007f2a5348e894 sp 00007fff908c88e0 error 4 in libc-2.10.1.so[7f2a5342c000+14c000]

[1989275.127643] h1susitmyepics[25166]: segfault at 0 ip 00007f5905a59894 sp 00007fff20f878d0 error 4 in libc-2.10.1.so[7f59059f7000+14c000]

2016-10-23T14:51:50.62907 LOCKLOSS_SHUTTER_CHECK W: Traceback (most recent call last):

2016-10-23T14:51:50.62909 File "/ligo/apps/linux-x86_64/guardian-1.0.2/lib/python2.7/site-packages/guardian/worker.py", line 461, in run

2016-10-23T14:51:50.62910 retval = statefunc()

2016-10-23T14:51:50.62910 File "/opt/rtcds/userapps/release/isc/h1/guardian/LOCKLOSS_SHUTTER_CHECK.py", line 50, in run

2016-10-23T14:51:50.62911 gs13data = cdu.getdata(['H1:ISI-HAM6_BLND_GS13Z_IN1_DQ','H1:SYS-MOTION_C_SHUTTER_G_TRIGGER_VOLTS'],12,self.timenow-10)

2016-10-23T14:51:50.62911 File "/ligo/apps/linux-x86_64/cdsutils/lib/python2.7/site-packages/cdsutils/getdata.py", line 78, in getdata

2016-10-23T14:51:50.62912 for buf in conn.iterate(*args):

2016-10-23T14:51:50.62912 RuntimeError: Requested data were not found.

2016-10-23T14:51:50.62913

Started Beckhoff SDF for h1ecatc1 PLC2, h1ecatx1 PLC2, and h1ecaty1 PLC2 by following the instructions at the end of this wiki: https://lhocds.ligo-wa.caltech.edu/wiki/UpdateChanListBeckhoffSDFSystems controls@h1build ~ 0$ starth1sysecatc1plc2sdf h1sysecatc1plc2sdfepics: no process found Specified filename iocH1.log does not exist. h1sysecatc1plc2sdfepics H1 IOC Server started controls@h1build ~ 0$ starth1sysecatx1plc2sdf h1sysecatx1plc2sdfepics: no process found Specified filename iocH1.log does not exist. h1sysecatx1plc2sdfepics H1 IOC Server started controls@h1build ~ 0$ starth1sysecaty1plc2sdf h1sysecaty1plc2sdfepics: no process found Specified filename iocH1.log does not exist. h1sysecaty1plc2sdfepics H1 IOC Server started

Everything was going well until 10 minutes before the end of the shift. The IFO was locked at NLN (26 W) and the range was fairly steady around 60 Mpc. Then at 14:50 UTC the IFO lost lock, guardian went into error, and it looks like various frontend models have crashed. 08:06 UTC Stefan done commissioning. IFO is locked at NLN (26 W) 14:50 UTC Lock loss. ISC_LOCK node in error. LOCK_LOSS_SHUTTER_CHECK node in error. Hit load on ISC_LOCK. Lots of voice alarms. Various frontend models are white.

Ed, Patrick 14:50 UTC The IFO lost lock. Guardian reported ISC_LOCK node in error and LOCK_LOSS_SHUTTER_CHECK node in error. The guardian overview turned dark red. I hit LOAD on the ISC_LOCK guardian. Ed came in and I turned around and saw a bunch of frontend models were white. I thought it must have been a power glitch, so I called Richard. He reported that he did not receive any notices related to a power problem and suggested I call Dave. I have done so, but have not been able to reach him yet. I am no longer thinking it is a power glitch. The laser is still up and all of the machines in the MSR appear to be running. I have attached a screenshot of the initial guardian error and the cds overview.

This spectrum was taken with the POP_A PIT QPD offset removed (see snapshots).

Left plot: Current noise agains O1-references.

Right plot: Current noise against tonight's 40W noise, and the noise from last night (POP_A PIT QPD offset was on, TCS ringheater was transitioning - see previous elog.)

Plot 1 shows the DC signals of all 4 I segments of ASA36. Note that seg 3 is ~2.5 times larger than the others.

Plot 2 shows the updated AS_A_RF36_I matrix - the gains for seg 3 have been dropped to -0.4 from -1.

Plot 3 shows the resulting error signal - it now cresses zero where the buildups and couplings for SRCL are good.

Closed the SRC1 PIT and YAW loops with a gain of 10, and input matrix element of 1. I will leave this setting for the night - although it is not in guardian yet.

I accepted the funny matrix in SDF, and added this in the SRM ASC high power state. The loops should only come on for input powers less than 35 Watts. Nutsinee and I tested it once.

Stefan, Terra

We had a large peak rise quickly at 27.41 Hz around 6 UTC. A bit of searching gave us Jeff's alog identifying it as the bounce mode of PR2; as such we lowered gain of MICH from 2 --> 1.2 which eventually allowed it to ring down.

We were wondering whether the auxiliary noise depends on the TCS state or PR3 spot position. Last night we had a ringheater change with several short locks over the night, and tonight we had some alignment change.

Attached are AUX spectra from last night, from early tonight, and just now. For some reason the early tonight spectra were significantly better (albeit not quite O1 quality). We could not correlate it with alignment or heating in a systematic way.

TITLE: 10/22 Eve Shift: 23:00-07:00 UTC (16:00-00:00 PST), all times posted in UTC

STATE of H1: Commissioning

INCOMING OPERATOR: Patrick

SHIFT SUMMARY:

I would recomend that instead of putting the extra factor of 2 gain in PRCL2, people double the gain in PRCL 1. The guardian doesn't touch the gain in PRCL2, but it will later in the locking sequence adjsut PRCL1 to be the nominal value. If people adjust the gain in PRCL2 and forget to rest it to 1, this can cause problems.

If we consistently are needing higher gain, there is a parameter in LSC params that adjusts the gains for lock acquisition.