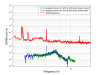

Today I was able to remeasure the frequency noise coupling into DARM. I am not finished analyzing the data, but as a preview I am attaching the TF of the IMC VCO to the DCPD sum above 1 kHz. The coupling appears to go like 1/f, or perhaps slightly faster. A 1/f coupling would be consistent with what was found previously (a flat coupling from REFL9I power to DCPD photocurrent).

I was not able to get coherence between my CARM excitation and the IMC VCO below 1 kHz.

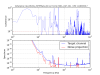

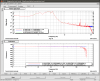

Attachment shows TF of demodulated REFL9 volts to DCPD sum (in milliamps). Compared to the previous measurement, the high-frequency portion is a factor of 3 higher. Additionally, we do not clearly see a transition to 1/f2 behavior around 250 Hz, as was seen in the last measurement. One might plausibly claim that the new measurement shows a knee around 100 Hz.

At 50 Hz, this TF predicts a frequency noise coupling that is a factor of 4 or so lower than the previous measurement.

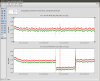

Additionally, during the measurement I noticed that the nonlinear coupling into DARM was quite significant from 40 to 100 Hz; we could see broad wings around the excitation frequency.