Keita, Evan, Hugh, Kiwamu,

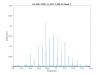

When clearing the SDF differences, we noticed that the pitch bias offset of IM1, 2 and 3 are very different from the past (by ~ 1000 urad). These new offsets are the results of an alignment recovery effort by Cheryl at around 2 pm PT yesterday.

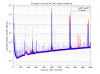

We checked various trends to understand why IMs needed so much change in the bias, but no clue was found. In the end, we accepted the new IM alignments even though we do not understand why they had moved. See the attached for the SDF difference.

The recovery effort

It looks that yesterday Cheryl changed the bias of IM1, 2 and 3 in order to bring them back to a place where their OSEMs read the same alignment values. As written below, after the interferomter was fully locked in this morning, the relevant QPD signals indicated that the laser light hits the same postion in the HAM2 and HAM3 area. This means her alignment recovery really aligned the beam back to where it should be. Or, in other words, IMs really had moved during the power outage for some reason. We still do not know why IMs had moved.

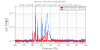

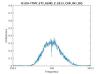

QPDs do not indicate a significant change

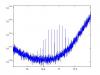

We checked the IM4 trans and POP_B QPDs in full lock to see if there is a significant difference in the actual laser beam. It seems that they are back to where they were in the past. This means that the interferomter alignment is not significantly different from the past with the new IM alignment. Good.

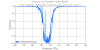

Also we looked at the HAM2 ISI oplev. Even though the oplev beam was not centered, we did not see a major change in PIT and YAW signals. They are about the same as before the power outage within a 1 urad.

Note that since POP_A is a part of the ASC control loop, it stayed centered.

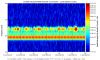

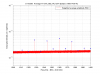

HEPI and ISI

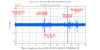

With help from Hugh, we checked HAM2 HEPI and ISI to see if they are back to nominal. And they are the same as before except for two HEPI prignle modes. See the attached for a trend of HEPI position locations. The HP mode moved by 5e5 (nm?) and VP mode changed by 3.5e3 (nm?). We are not sure how significant these numbers are in terms of the ISI table alginement.

Note that since the pringle modes are not DC-controlled and therefore it is sort of natural that they did not come back to where they used to be.