Back to locking robustly, all the way to Nominal Low Noise. Hooray!

It was a bit of a trying day, locking-wise. Jim was a champ, trying to get it back up after the many, many locklosses throughout the day. We have made several changes to the guardian scripts that seem to be helping immensely. Here are the changes that were made:

-

Slower CARM offset reduction in Switch to QPDs.

- Toward the end of the day, we were losing the lock (6+ times in a row!) during the CARM offset steps. Sheila and I did the Switch to QPDs step by hand, in several smaller steps, which was immediately successful.

- We doubled the ramp time for the final CARM offset reduction, and have now successfully gone through the sequence several times.

-

Lower DHARD Pitch gain.

- Several locklosses early in the day were due to oscillations in the DHARD pitch loop, which is modified at the beginning of Noise Tunings.

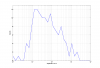

- We measured the DHARD loop, and found that the gain was a factor of 2 too high. The ELP33 cutoff filter eats enough phase that, in combination with the too-high gain, we were unstable.

- The DHARD gain increase from 10 to 20 in the Lownoise ETMY ESD state was commented out. The overall gain of DHARD Pitch is now correct, with the UGF appropriately around 3 Hz.

- The ELP33 in FM10 turn-on has been removed from the Noise Tunings state. Now that the gain has been measured and corrected, we can probably put it back, but I'm leaving it out for now, since I can't stay to test it.

-

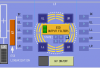

ITM oplevs left on.

- It was decided over the weekend that the ITM oplevs need to be left on, for stability, until we can finish tuning up the ASC loops. However, I found that they were still being turned off in the Noise Tunings state. This may not have been causing locklosses, but until we can verify this, we're commenting this out. So, now the oplevs for the ITMs are actually left on.

-

OMC DCPD whitening back in guardian.

- Due to the giganic violin modes over the last week, the turn-on of the OMC DCPD had been commented out of the guardian. Since we have successfully locked with it turned on by hand, I've added it back to the guardian. Our range (according to SensMon) is back above 60 Mpc. Nice.

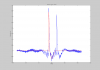

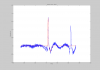

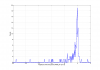

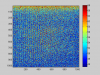

As an aside, I happened to notice some transients in the ETMX L3 ESD AMON channels pass by on Dataviewer, and looked into them a bit. These transients happened while we were turning off the ETMX ESD after transitioning to the ETMY. Thankfully, we didn't lose lock, but I post the time series of the transients anyway. You'll notice in the attached plot that we basically see no effect in DARM, although I should put these channels through the new lockloss tool from Hang, et al. to see if there are any high-frequency things in DARM that are being swamped by the low-f stuff.