Summary

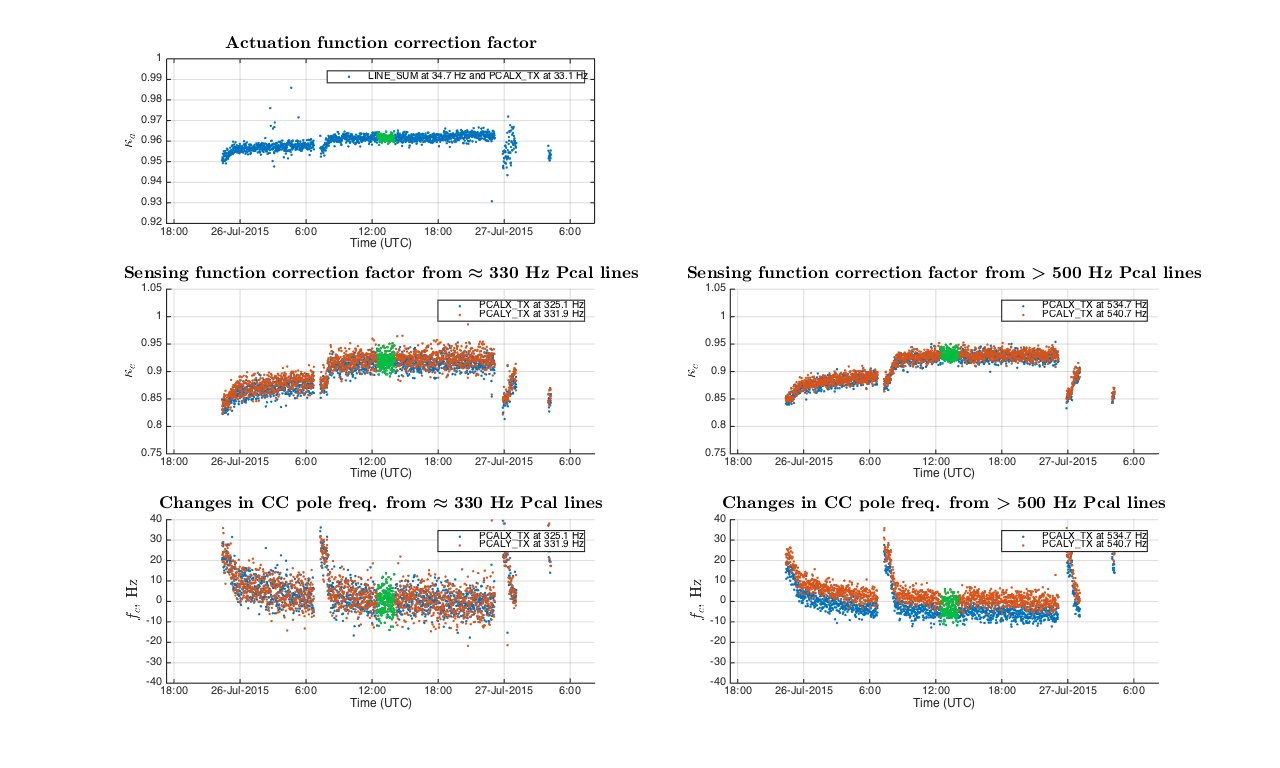

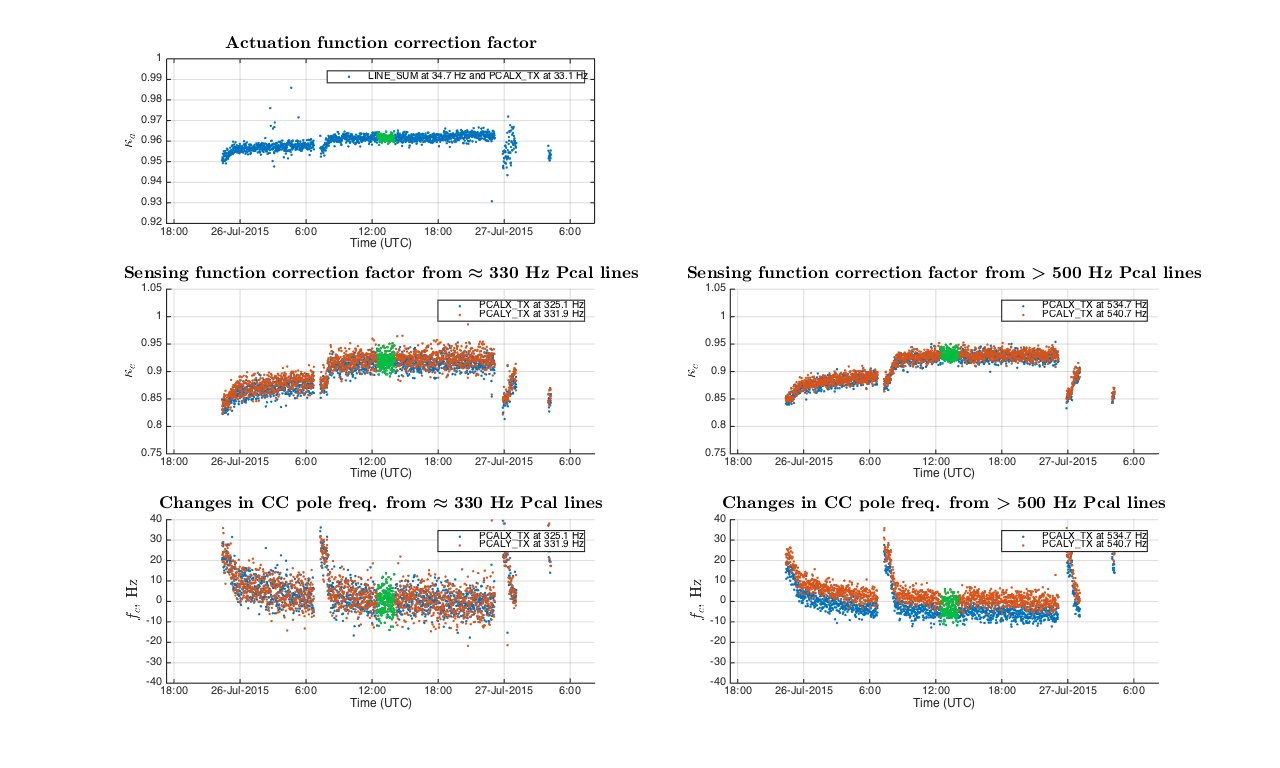

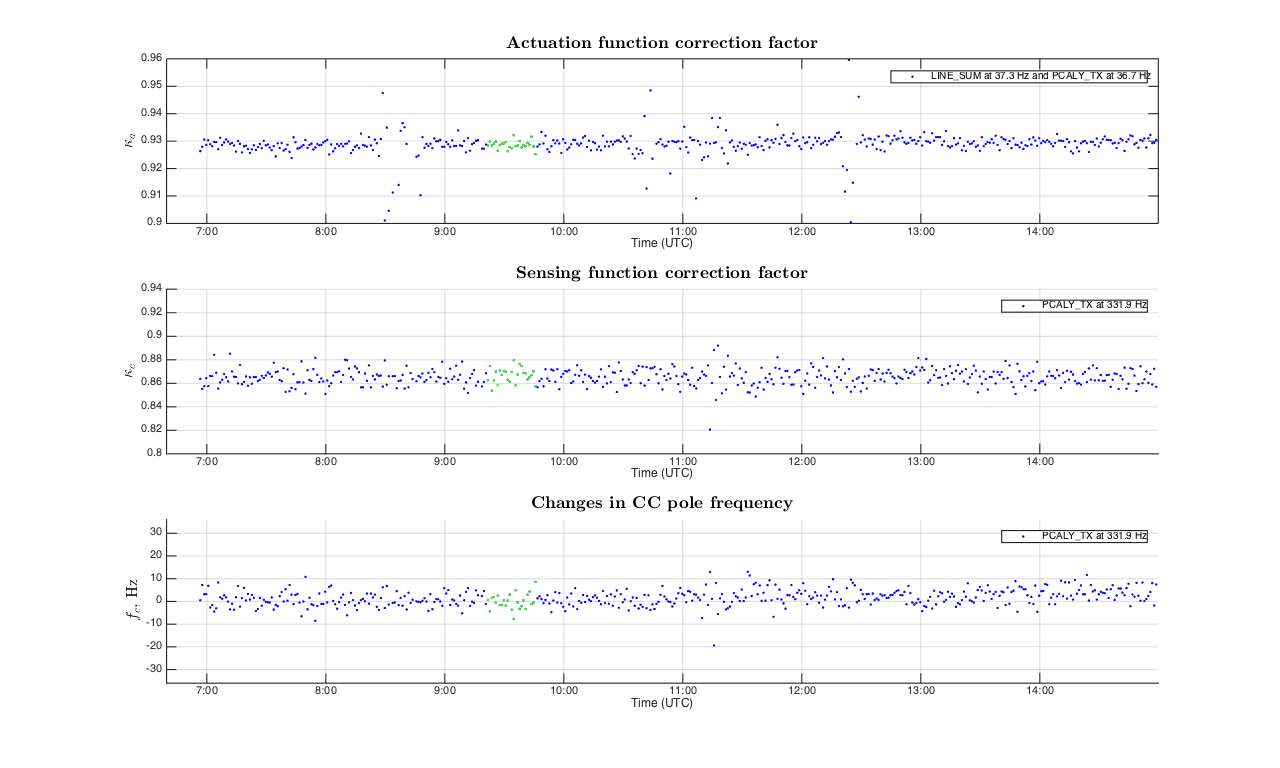

To decrease uncertainty in calculation of actuation function correction factor, kappa_A, sensing function correction factor, kappa_C, and CC pole frequency, f_c, we've recently increased calibration line amplitudes to give SNR of 100 with 10s FFT (see LHO alog #19792). Earlier Kiwamu posted his investigation of CC pole frequency over the last weekend in LHO alog comment #19988. In this alog we show kappa_A, kappa_C and f_c calculated according to the method described in T1500377-v3 for the same time interval (2015-07-25 00:00 UTC to 2015-07-27 UTC, when GRD-ISC_LOCK_STATE_N >= 501, 1 min FFTs).

Statistical uncertainties of kappa_A, kappa_C and f_c within 1.5 hours time interval highlighted with green are:

Xctrl(34.7) and PcalX(33.1), std(kappa_A) = +/- 0.45 % (1 sigma)

PcalX(325.1), std(kappa_C) = +/- 1.12 % (1 sigma); std(f_c) = +/- 5.20 Hz (1 sigma)

PcalY(331.9), std(kappa_C) = +/- 1.43 % (1 sigma); std(f_c) = +/- 5.55 Hz (1 sigma)

PcalX(534.7), std(kappa_C) = +/- 0.70 % (1 sigma); std(f_c) = +/- 2.08 Hz (1 sigma)

PcalY(540.7), std(kappa_C) = +/- 0.78 % (1 sigma); std(f_c) = +/- 2.68 Hz (1 sigma)

Notice that kappa_C and f_c on the left subplots were calculated from low SNR 325.1 Hz and 331.9 Hz Pcal lines set by Evan (see LHO alog comment #19823). Calculation of these parameters using higher SNR 534.7 Hz and 540.7 Hz Pcal lines (right subplots) gave less noisy results.

Details

C_0, D_0 and A_0 were taken from LHO ER7 DARM model.

To make kappa_C calcluations consistent between results from 4 Pcal lines, a manual correction to phases of Pcal lines that correspond to 130us of time advance was applied. On the plot we report only changes in f_c by subtracting mean value of about 300 Hz. In order to receive an absolute value of f_c using this method, we must take into account exact time delay/advance of PCAL RXPD channel w.r.t. DARM_ERR; possibly a frequency independent phase shift (however we do now know any reason for that); and the DARM model TFs at the reference time, C_0, D_0 and A_0.

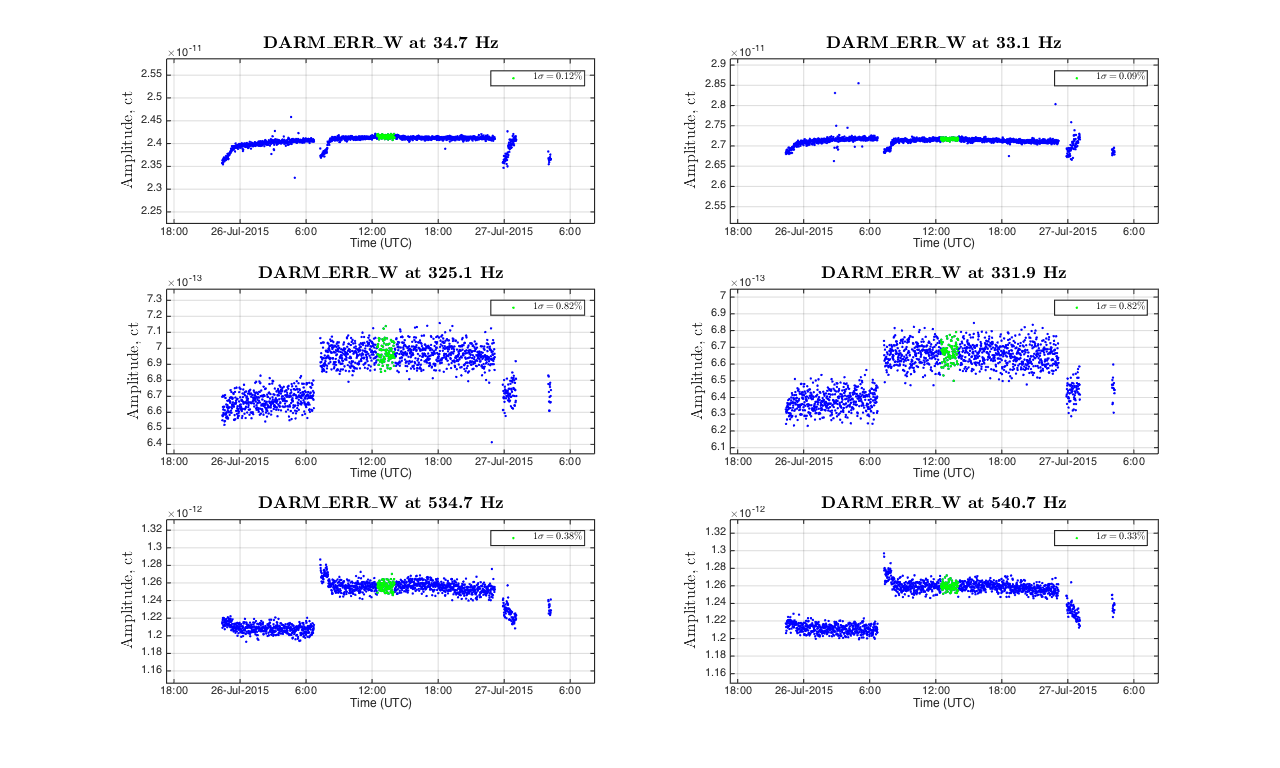

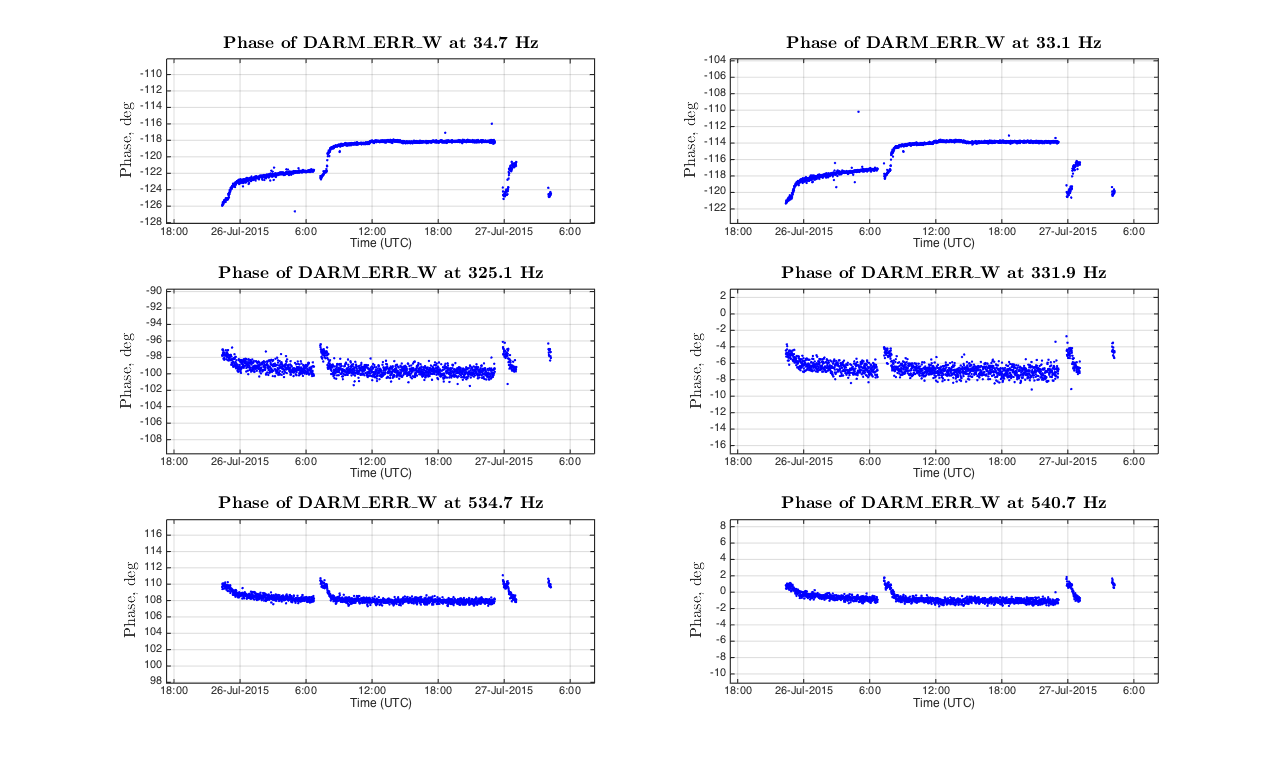

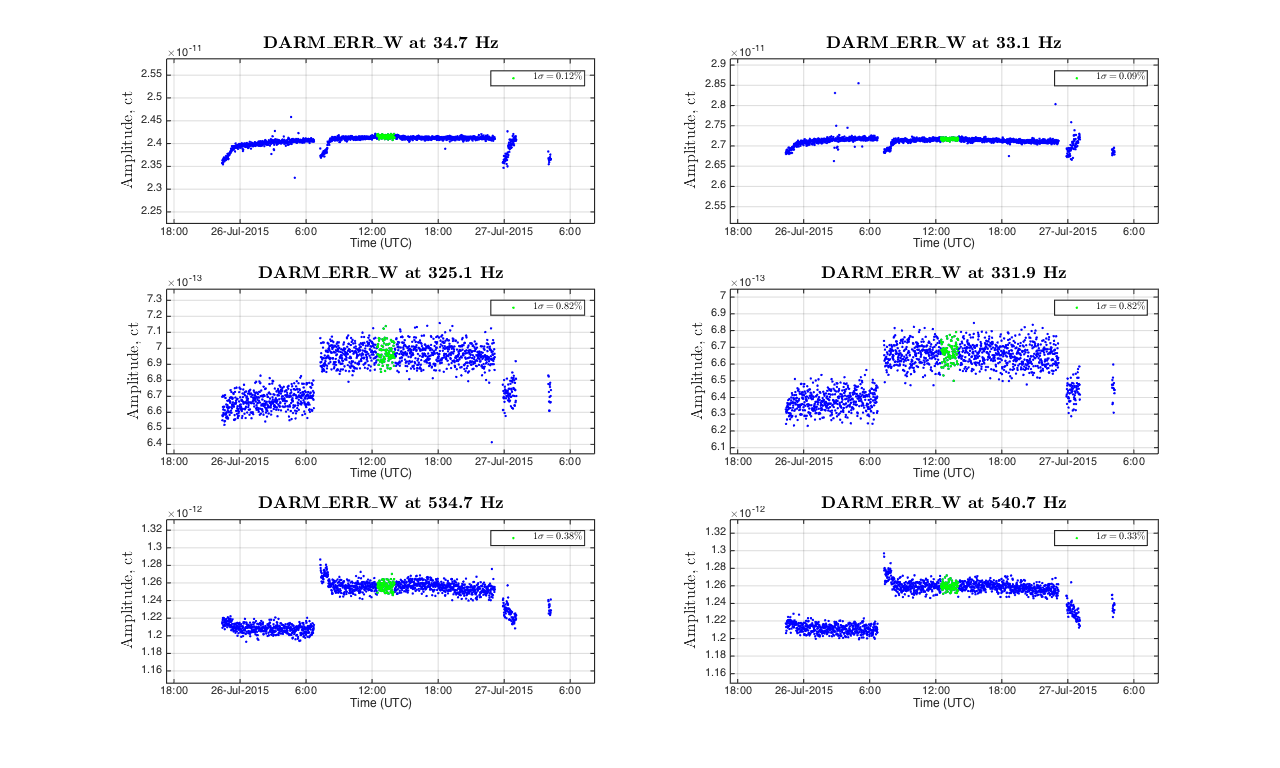

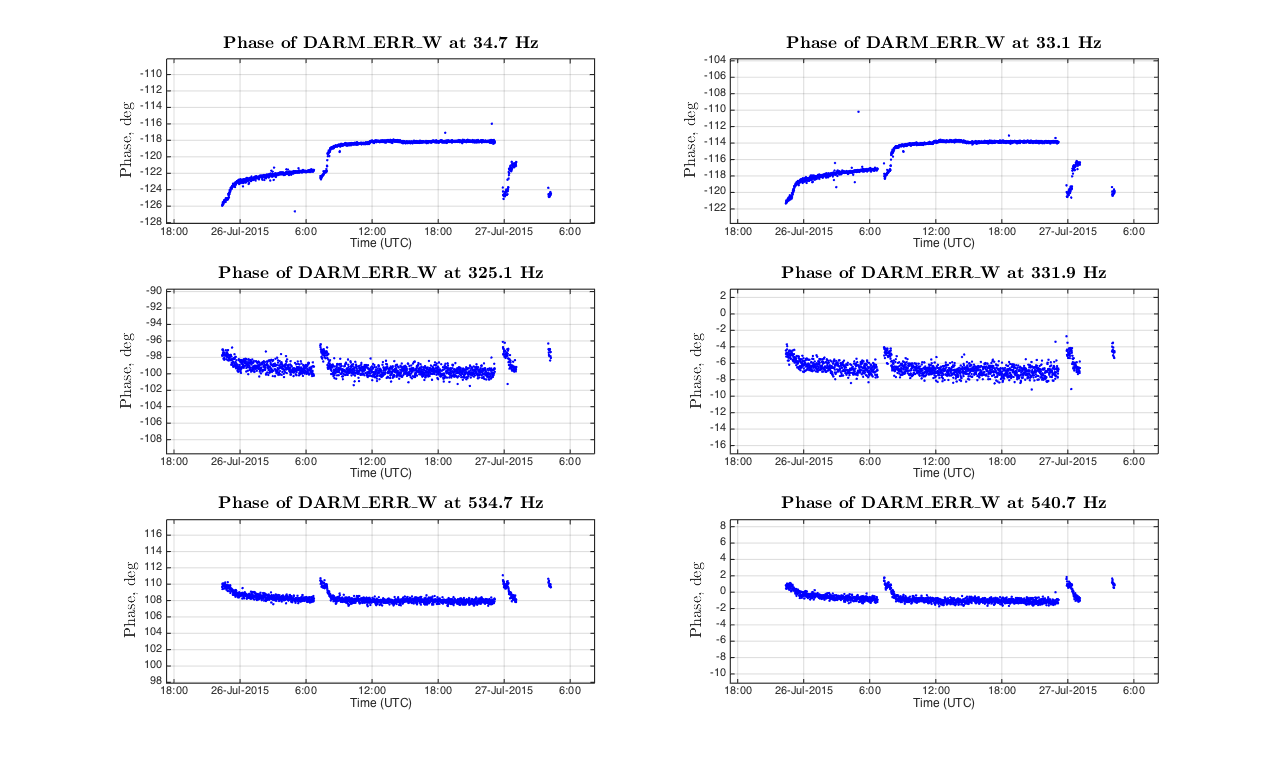

Plots of 1 min FFT dewhitened calibration line amplitudes and phases are given below.

Calibration line uncertainties in DARM_ERR readout in a 1.5 hours interval (highlighted with green color) are as follows:

Xctrl( 34.7) = 2.2000e-01 (+/- 0.00 %); Derr( 34.7) = 2.9738e-10 (+/- 0.15 %)

PcalX( 33.1) = 2.4587e-02 (+/- 0.00 %); Derr( 33.1) = 3.0817e-10 (+/- 0.26 %)

PcalX(325.1) = 1.0724e-01 (+/- 0.00 %); Derr(325.1) = 2.0593e-10 (+/- 1.48 %)

PcalY(331.9) = 9.3791e-02 (+/- 0.01 %); Derr(331.9) = 2.0150e-10 (+/- 1.55 %)

PcalX(534.7) = 7.1100e-01 (+/- 0.00 %); Derr(534.7) = 5.8223e-10 (+/- 0.52 %)

PcalY(540.7) = 6.3845e-01 (+/- 0.01 %); Derr(540.7) = 5.8948e-10 (+/- 0.45 %)

P.S.

After today's calibration telecon we've changed calibration lines that will be used for estimation of kappa_A, kappa_C and f_c to (see LHO alog #20063):

-

PCALY 36.7 Hz, SNR ~100;

-

DARM_CTRL 37.3 Hz, SNR ~90;

-

PCALY 331.9 Hz, SNR~100;

-

PCALY 1083.7 Hz, SNR~40;

We are also planning to add an ESD line close to low frequency PCALY line and another high frequency low SNR PCALX line at 3001.3 Hz after completing power budget investigations of PCALX module.

I did injections into MICH (from 10:41:40 to 10:47:00) and SRCL (from 11:15:00 to 11:22:40) with all FF on.

About 30 s after turning off the SRCL injection, a number of photodiode signals associated with the AS port dropped suddenly by about 5% (in particular: AS DC, AS90, ASA sum, ASB sum, ASC sum, and AS45Q; notably, the OMC DCPDs, POP DC, MC2 sum, and IMC input power did not see this). After that, the interferometer glitched for about 30 minutes. This event happened at 11:23:31.05 and lasted for only a few milliseconds.

I did an injection into PRCL (from 12:21:50 to 12:29:00).

I did an injection into the ISS around 12:52:00. I think this measurement needs to be redone by injecting into the error point of the outer loop rather than the inner loop. With the outer loop closed it is now difficult to get good coherence between intensity and DARM below 300 Hz.

PSL Peri PZT servo ON/OFF test:

IFO was still locked when I came in in the morning, so I briefly switched the IMC WFSB YAW to PSL PZT feedback path at around 7:50 AM local time.

In the attached, references are with the servo on, current traces are without the servo.

Middle finger (300Hz bump) is greatly reduced in OMC DCPD, but the coherence for right and index finger slightly increased due to gain peaking (expected), and there is another gain peaking at 620Hz (again expected). The last one could be reduced further by adding a deeper notch but that might increase the 350Hz bump gain peaking a bit.

The servo was turned on again at about 8AM+-5min.