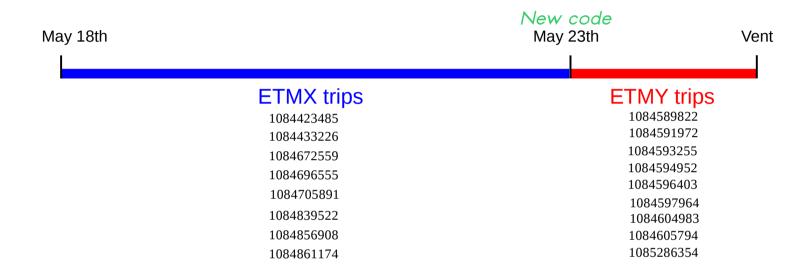

### Lock loss at LHO

Trips due to lock loss  $\rightarrow$  2 distinct phases

All the ETMX trips present the same symptoms. All the ETMY trips present the same symptoms.

Starting with ETMX

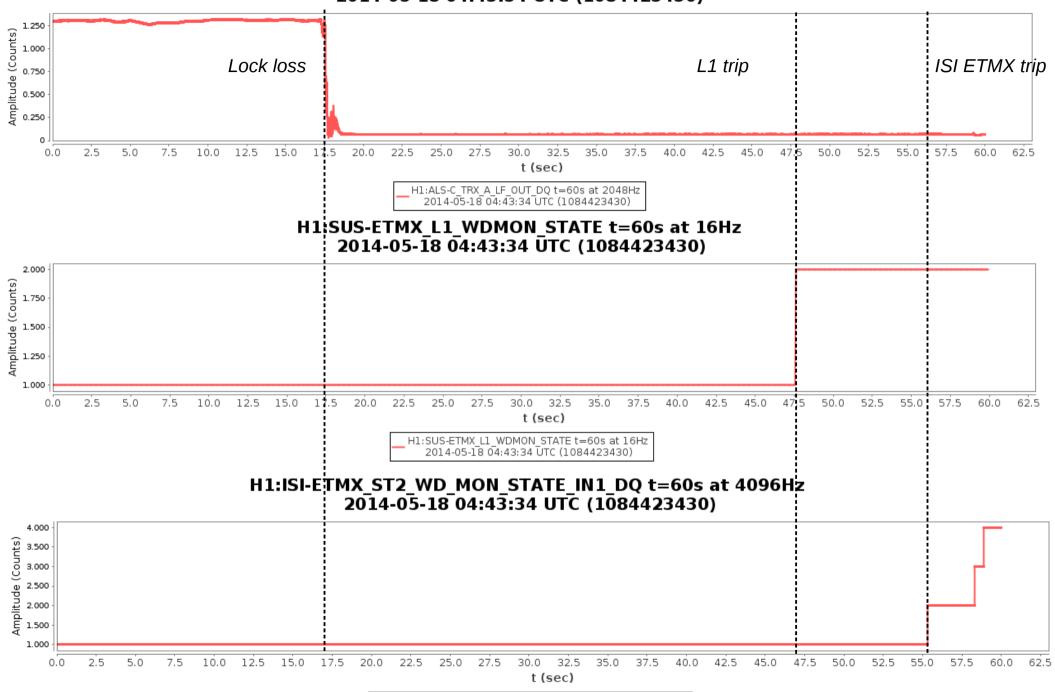

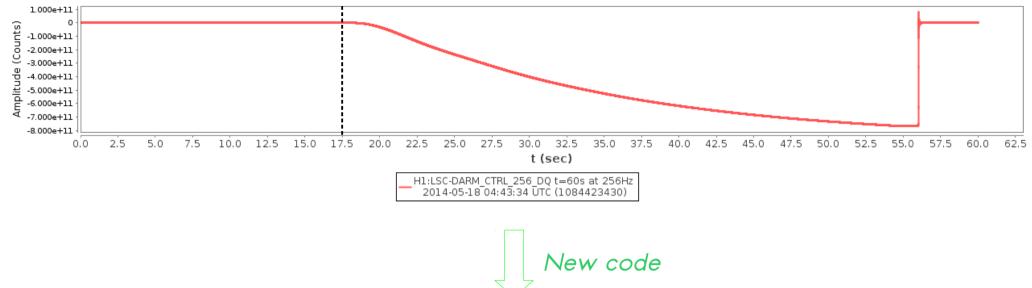

### H1:ALS-C\_TRX\_A\_LF\_OUT\_DQ t=60s at 2048Hz 2014-05-18 04:43:34 UTC (1084423430)

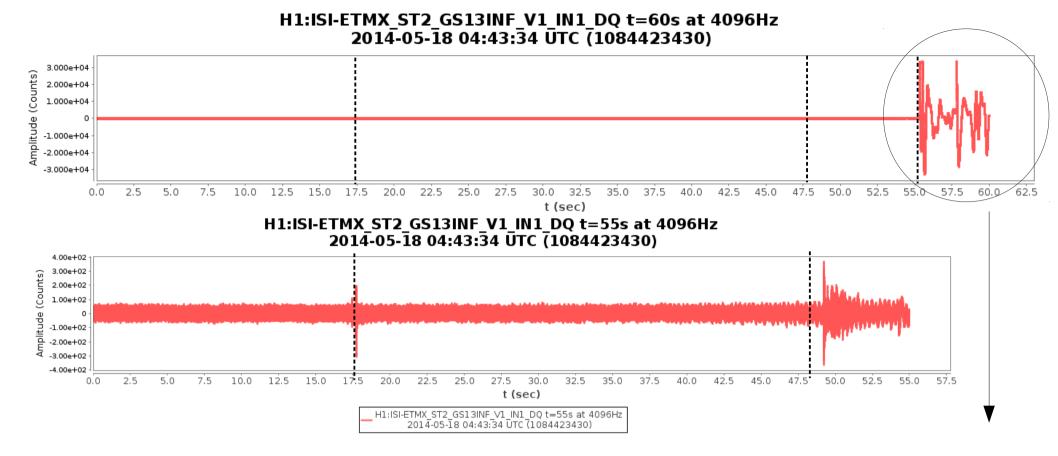

H1:ISI-ETMX\_ST2\_WD\_MON\_STATE\_IN1\_DQ t=60s at 4096Hz 2014-05-18 04:43:34 UTC (1084423430)

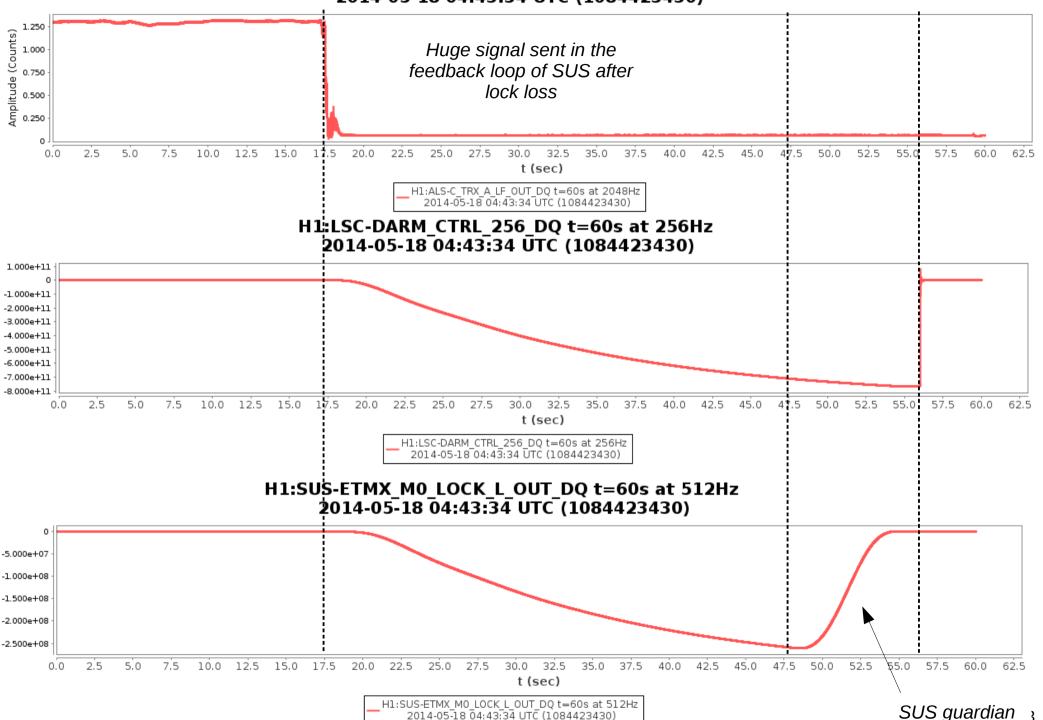

### H1:ALS-C TRX A LF OUT DQ t=60s at 2048Hz 2014-05-18 04:43:34 UTC (1084423430)

SUS guardian 3

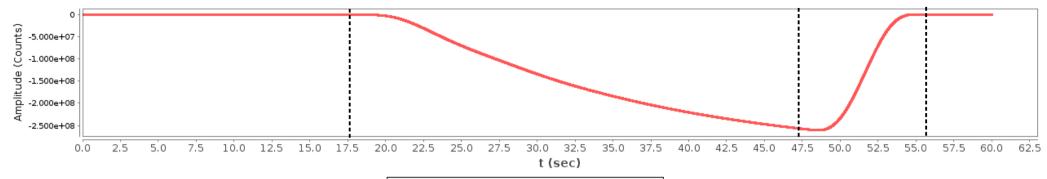

# H1:SUS-ETMX\_M0\_LOCK\_L\_OUT\_DQ t=60s at 512Hz 2014-05-18 04:43:34 UTC (1084423430)

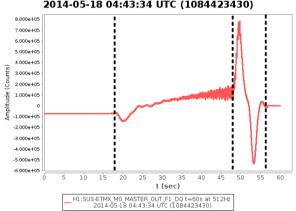

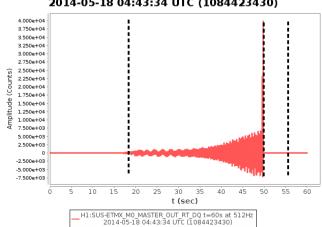

#### HI:SUS-EIMX MU MASIEK UUI FI DU T=DUS AT 312HZ 2014-05-18 04:43:34 UTC (1084423430)

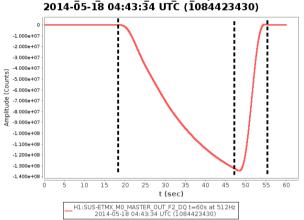

#### H1:SUS-ETMX M0 LOCK L OUT D0 t=60s at 512Hz 2014-05-18 04:43:34 UTC (1084423430) HI:SUS-EIMX MO MASIER OUI F2 DQ t=60s at 512Hz

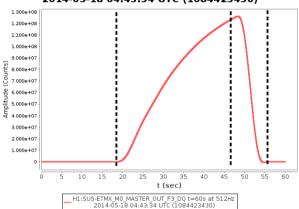

#### HI:5U5-EIMX MU MASIEK UUI F3 DQ T=bUS aT 512HZ 2014-05-18 04:43:34 UTC (1084423430)

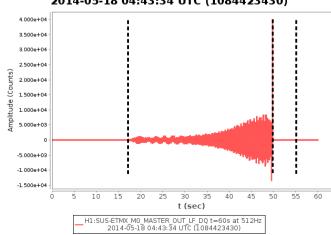

H1:SUS-ETMX M0 MASTER OUT LF DQ t=60s at 512Hz 2014-05-18 04:43:34 UTC (1084423430)

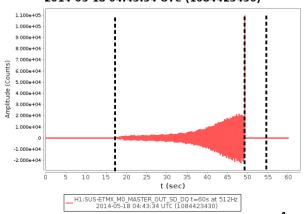

H1:SUS-ETMX M0 MASTER OUT RT DQ t=60s at 512Hz 2014-05-18 04:43:34 UTC (1084423430)

H1:SUS-ETMX M0 MASTER OUT SD DQ t=60s at 512Hz 2014-05-18 04:43:34 UTC (1084423430)

# H1:SUS-ETMX\_L1\_LOCK\_L\_OUT\_DQ t=60s at 1024Hz 2014-05-18 04:43:34 UTC (1084423430)

\_\_H1:SUS-ETMX\_L1\_LOCK\_L\_OUT\_DQ t=60s at 1024Hz 2014-05-18 04:43:34 UTC (1084423430)

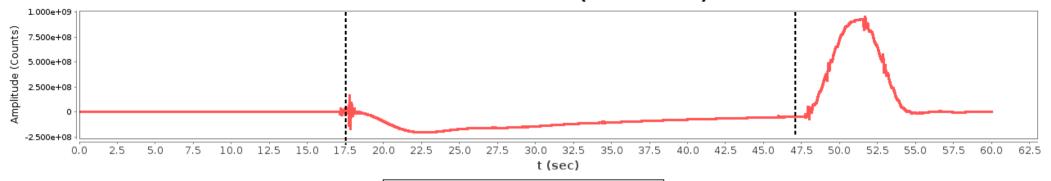

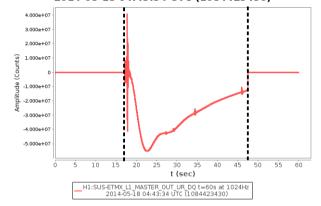

## H1:SUS-ETMX\_L1\_MASTER\_OUT\_UR\_DQ t=60s at 1024Hz 2014-05-18 04:43:34 UTC (1084423430)

### H1:SUS-ETMX L1 MASTER OUT LL DQ t=60s at 1024Hz 2014-05-18 04:43:34 UTC (1084423430)

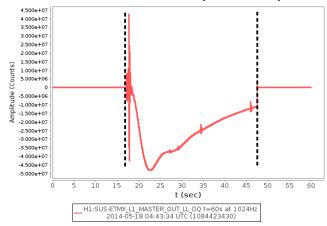

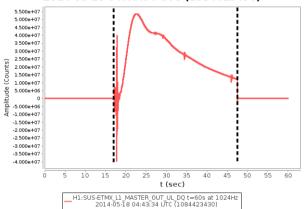

### H1:SUS-ETMX\_L1\_MASTER\_OUT\_UL\_DQ t=60s at 1024Hz 2014-05-18 04:43:34 UTC (1084423430)

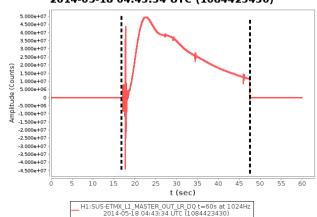

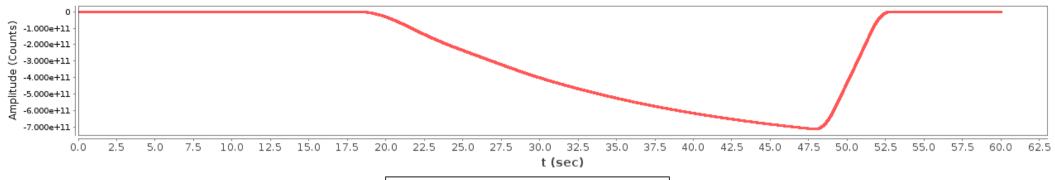

### H1:SUS-ETMX L1 MASTER OUT LR DQ t=60s at 1024Hz 2014-05-18 04:43:34 UTC (1084423430)

# H1:SUS-ETMX\_L2\_LOCK\_L\_OUT\_DQ t=60s at 2048Hz 2014-05-18 04:43:34 UTC (1084423430)

### H1:SUS-ETMX\_L2\_MASTER\_OUT\_UL\_DQ t=60s at 2048Hz 2014-05-18 04:43:34 UTC (1084423430)

## H1:SUS-ETMX\_L2\_MASTER\_OUT\_UR\_DQ t=60s at 2048Hz 2014-05-18 04-43-34 UTC (1084423430)

### H1:SUS-ETMX\_L2\_MASTER\_OUT\_LL\_DQ t=60s at 2048Hz 2014-05-18 04:43:34 UTC (1084423430)

### H1:SUS-ETMX L2 MASTER OUT LR DQ t=60s at 2048Hz 2014-05-18 04:43:34 UTC (1084423430)

Nothing sent on L2

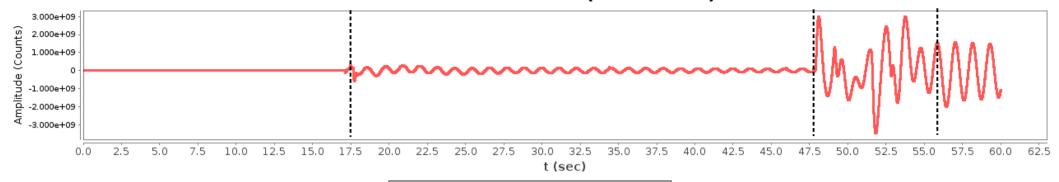

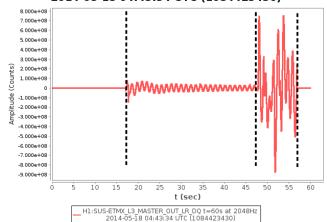

### H1:SUS-ETMX\_L3\_LOCK\_L\_OUT\_DQ t=60s at 2048Hz 2014-05-18 04:43:34 UTC (1084423430)

H1:SUS-ETMX L3 LOCK L OUT DQ t=60s at 2048Hz 2014-05-18-04:43:34 UTC (1084423430)

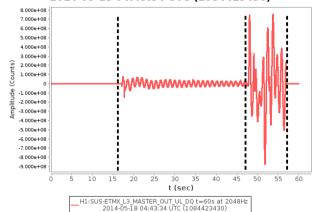

#### H1:SUS-ETMX L3 MASTER OUT UL DQ t=60s at 2048Hz 2014-05-18 04:43:34 UTC (1084423430)

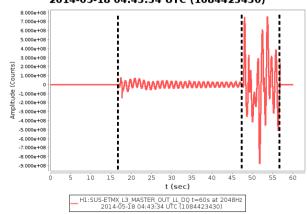

#### H1:SUS-ETMX L3 MASTER OUT LL DQ t=60s at 2048Hz 2014-05-18 04:43:34 UTC (1084423430)

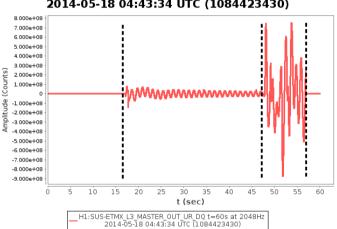

#### H1:SUS-ETMX L3 MASTER OUT UR DQ t=60s at 2048Hz 2014-05-18 04:43:34 UTC (1084423430)

#### H1:SUS-ETMX L3 MASTER OUT LR DQ t=60s at 2048Hz 2014-05-18 04:43:34 UTC (1084423430)

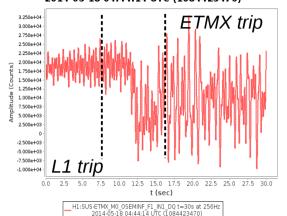

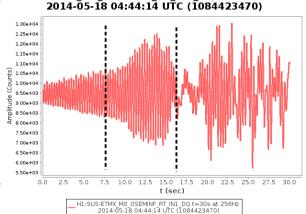

#### H1:SUS-ETMX M0 OSEMINF F1 IN1 DQ t=30s at 256Hz 2014-05-18 04:44:14 UTC (1084423470)

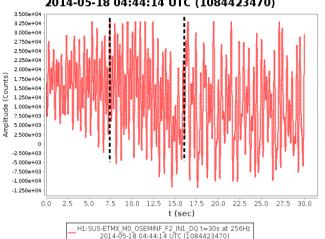

#### H1:SUS-ETMX M0 OSEMINF F2 IN1 DQ t=30s at 256Hz 2014-05-18 04:44:14 UTC (1084423470)

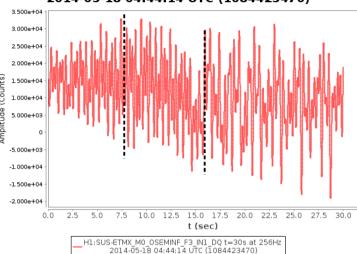

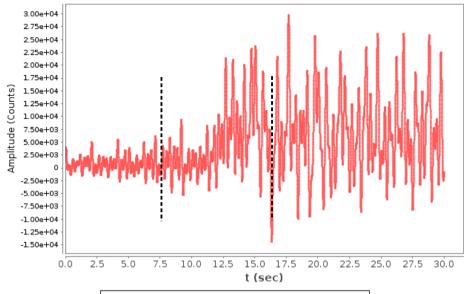

#### H1:SUS-ETMX M0 OSEMINF F3 IN1 DO t=30s at 256Hz 2014-05-18 04:44:14 UTC (1084423470)

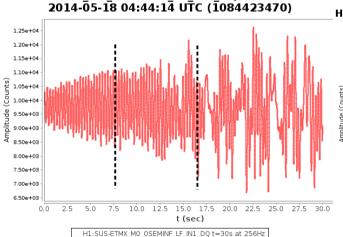

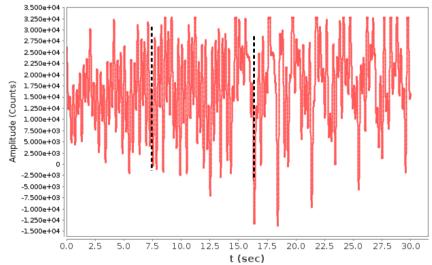

### H1:SUS-ETMX M0 OSEMINF LF IN1 DQ t=30s at 256Hz

2014-05-18 04:44:14 UTC (1084423470)

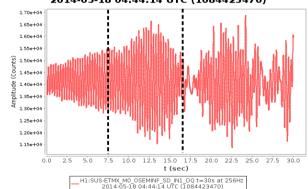

#### H1:SUS-ETMX M0 OSEMINF RT IN1 DO t=30s at 256Hz 2014-05-18 04:44:14 UTC (1084423470)

#### H1:SUS-ETMX M0 OSEMINF SD IN1 DQ t=30s at 256Hz 2014-05-18 04:44:14 UTC (1084423470)

## H1:SUS-ETMX\_L1\_OSEMINF\_UL\_IN1\_DQ t=30s at 256Hz 2014-05-18 04:44:14 UTC (1084423470)

H1:SUS-ETMX\_L1\_OSEMINF\_UL\_IN1\_DQ t=30s at 256Hz 2014-05-18 04:44:14 UTC (1084423470)

## H1:SUS-ETMX\_L1\_OSEMINF\_LL\_IN1\_DQ t=30s at 256Hz 2014-05-18 04:44:14 UTC (1084423470)

H1:SUS-ETMX\_L1\_OSEMINF\_LL\_IN1\_DQ t=30s at 256Hz 2014-05-18 04:44:14 UTC (1084423470)

## H1:SUS-ETMX L1 OSEMINF\_UR IN1\_DQ t=30s at 256Hz 2014-05-18 04:44:14 UTC (1084423470)

H1:SUS-ETMX\_L1\_OSEMINF\_UR\_IN1\_DQ t=30s at 256Hz 2014-05-18 04:44:14 UTC (1084423470)

## H1:SUS-ETMX\_L1\_OSEMINF\_LR\_IN1\_DQ t=30s at 256Hz 2014-05-18 04:44:14 UTC (1084423470)

H1:SUS-ETMX\_L1\_OSEMINF\_LR\_IN1\_DQ t=30s at 256Hz 2014-05-18 04:44:14 UTC (1084423470)

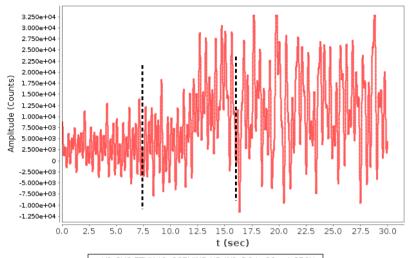

## H1:SUS-ETMX L2\_OSEMINF\_UL\_IN1\_DQ t=30s at 256Hz 2014-05-18 04:44:14 UTC (1084423470)

2014-05-18 04:44:14 UTC (1084423470)

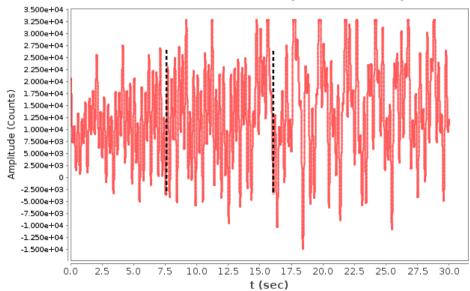

## H1:SUS-ETMX\_L2\_OSEMINF\_LL\_IN1\_DQ t=30s at 256Hz 2014-05-18 04:44:14 UTC (1084423470)

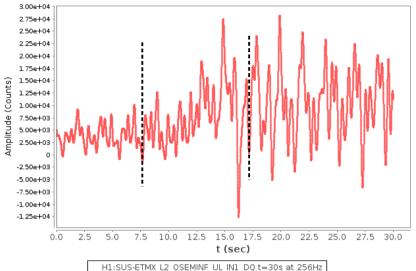

## H1:SUS-ETMX L2 OSEMINF\_UR IN1 DQ t=30s at 256Hz 2014-05-18 04:44:14 UTC (1084423470)

\_H1:SUS-ETMX\_L2\_OSEMINF\_UR\_IN1\_DQ t=30s at 256Hz 2014-05-18 04:44:14 UTC (1084423470)

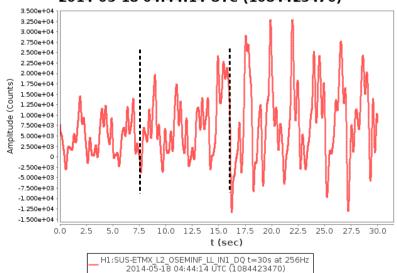

## H1:SUS-ETMX\_L2\_OSEMINF\_LR\_IN1\_DQ t=30s at 256Hz 2014-05-18 04:44:14 UTC (1084423470)

H1:SUS-ETMX\_L2\_OSEMINF\_LR\_IN1\_DQ t=30s at 256Hz 2014-05-18 04:44:14 UTC (1084423470)

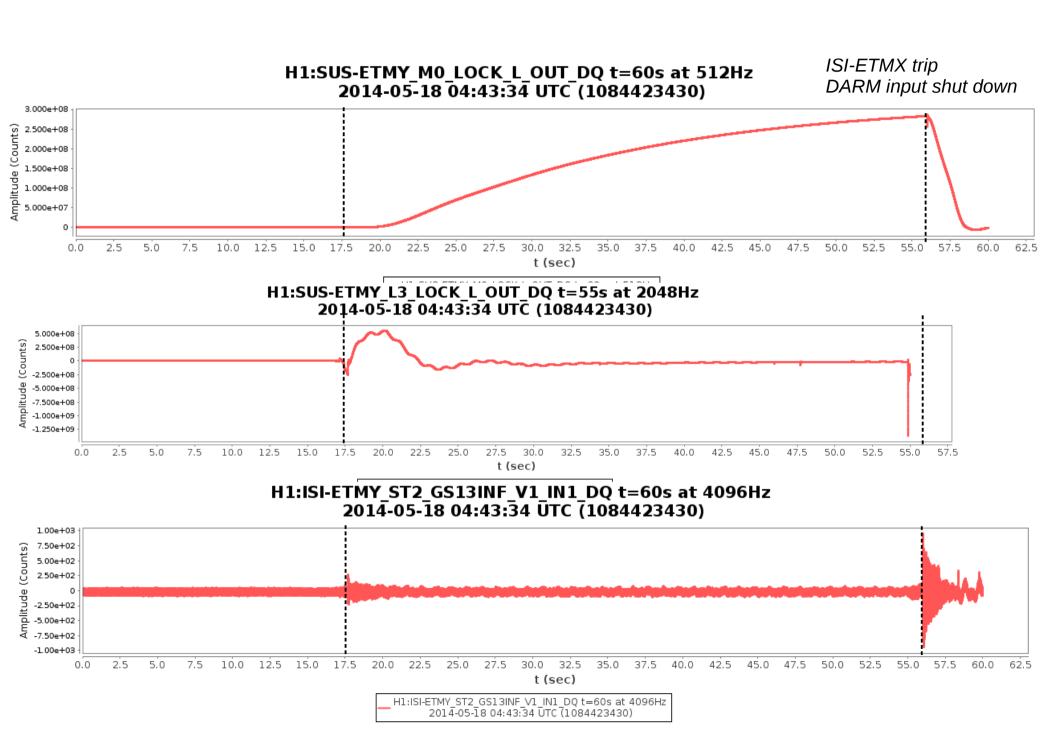

### Same behavior on ETMY (without the L1/ISI trip)

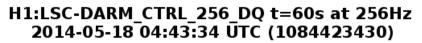

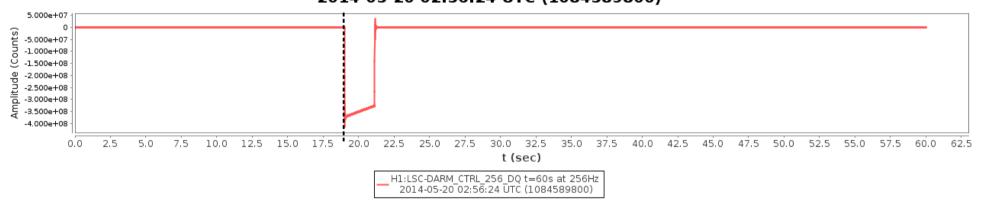

## H1:LSC-DARM\_CTRL\_256\_DQ t=60s at 256Hz 2014-05-20 02:56:24 UTC (1084589800)

Not perfect, but L1/ETMX are not tripping anymore

Let's have a look at ETMY

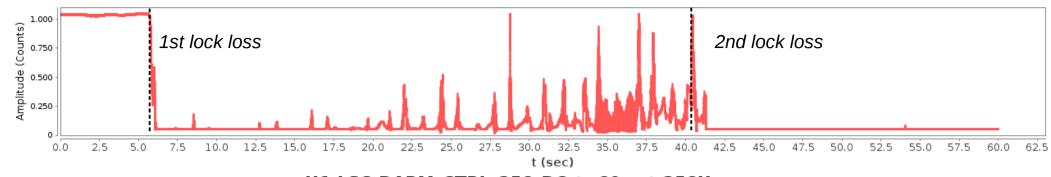

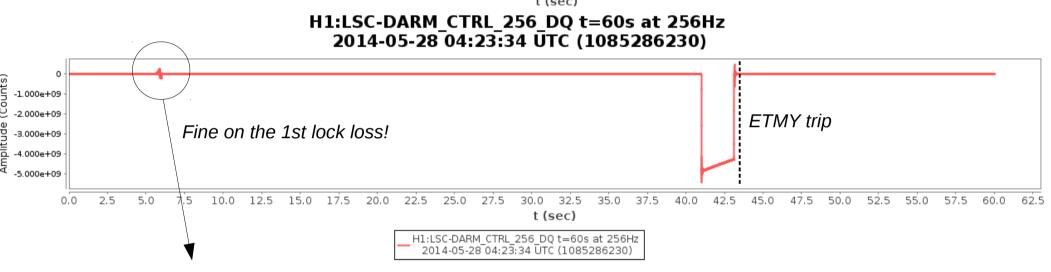

# H1:ALS-C\_TRX\_A\_LF\_OUT\_DQ t=60s at 2048Hz 2014-05-28 04:23:34 UTC (1085286230)

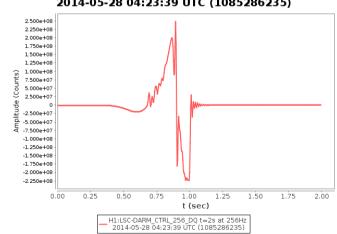

## H1:LSC-DARM\_CTRL\_256\_DQ t=2s at 256Hz 2014-05-28 04:23:39 UTC (1085286235)

Let's focus on the 2nd lock loss

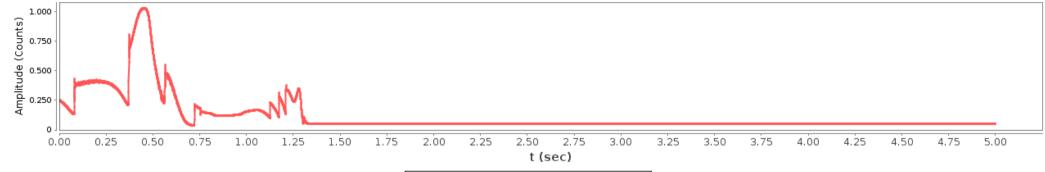

# H1:ALS-C\_TRX\_A\_LF\_OUT\_DQ t=5s at 2048Hz 2014-05-28 04:24:14 UTC (1085286270)

H1:ALS-C\_TRX\_A\_LF\_OUT\_DQ t=5s at 2048Hz 2014-05-28 04:24:14 UTC (1085286270)

2014-05-28 04:24:14 UTC (1085286270)

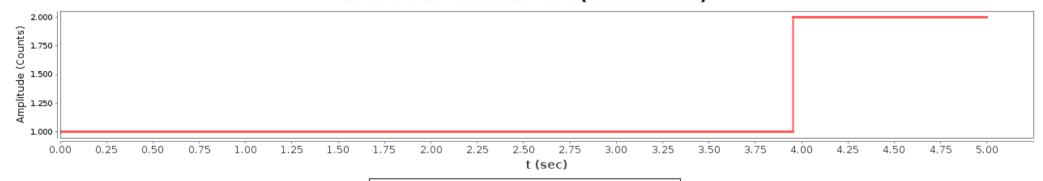

H1:ISI-ETMY\_ST2\_WD\_MON\_STATE\_IN1\_DQ t=5s at 4096Hz 2014-05-28 04:24:14 UTC (1085286270)

H1:ISI-ETMY\_ST2\_WD\_MON\_STATE\_IN1\_DQ t=5s at 4096Hz 2014-05-28 04:24:14 UTC (1085286270)

15

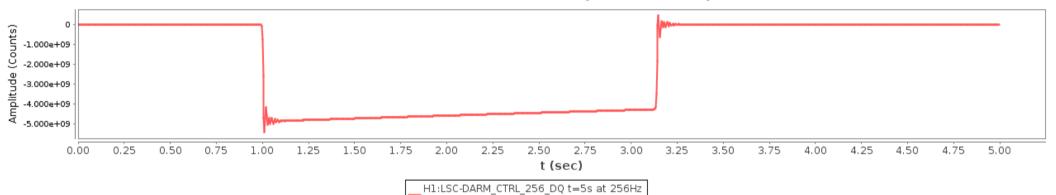

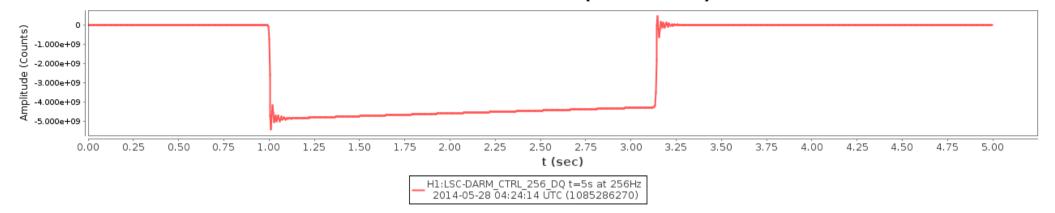

## H1:LSC-DARM\_CTRL\_256\_DQ t=5s at 256Hz 2014-05-28 04:24:14 UTC (1085286270)

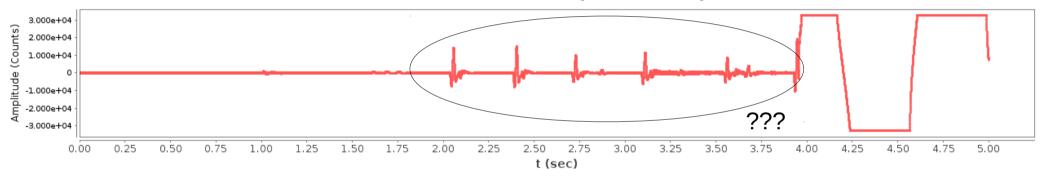

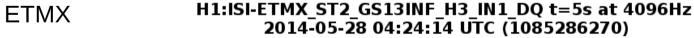

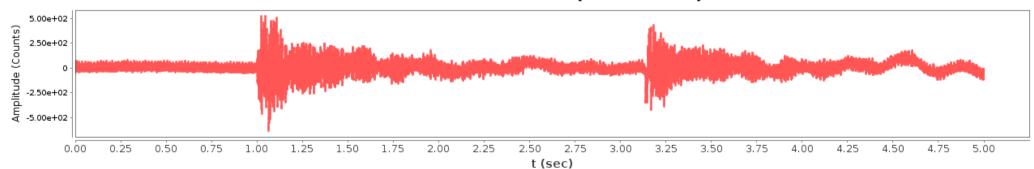

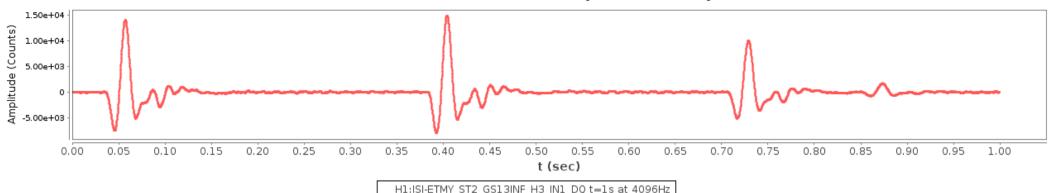

# ETMY H1:ISI-ETMY\_ST2\_GS13INF\_H3\_IN1\_DQ t=5s at 4096Hz 2014-05-28 04:24:14 UTC (1085286270)

\_\_H1:ISI-ETMY\_ST2\_GS13INF\_H3\_IN1\_DQ t=5s at 4096Hz 2014-05-28 04:24:14 UTC (1085286270)

H1:ISI-ETMX\_ST2\_GS13INF\_H3\_IN1\_DQ t=5s at 4096Hz 2014-05-28 04:24:14 UTC (1085286270)

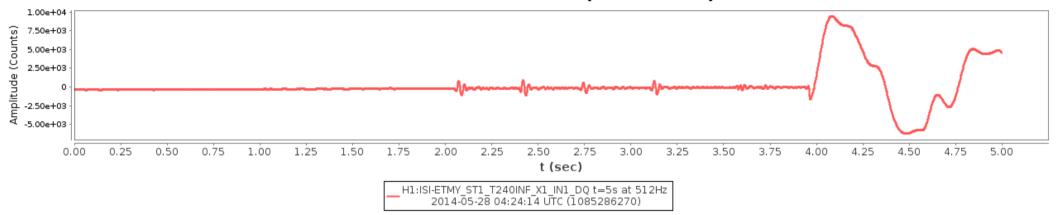

# H1:ISI-ETMY\_ST1\_T240INF\_X1\_IN1\_DQ t=5s at 512Hz 2014-05-28 04:24:14 UTC (1085286270)

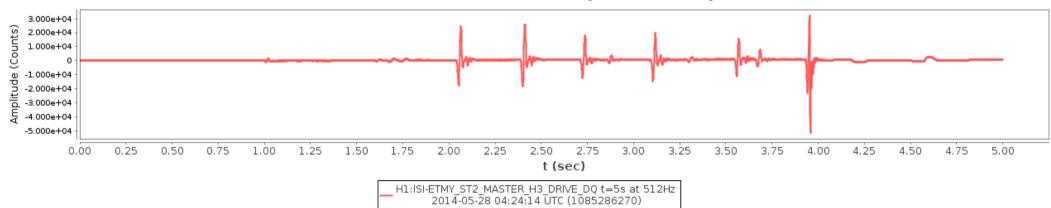

# H1:ISI-ETMY\_ST2\_MASTER\_H3\_DRIVE\_DQ t=5s at 512Hz 2014-05-28 04:24:14 UTC (1085286270)

What about SUS?

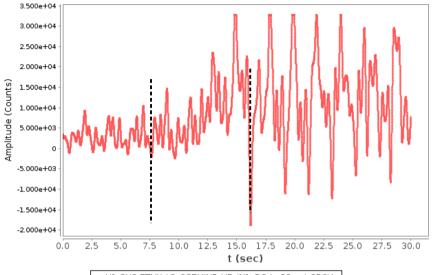

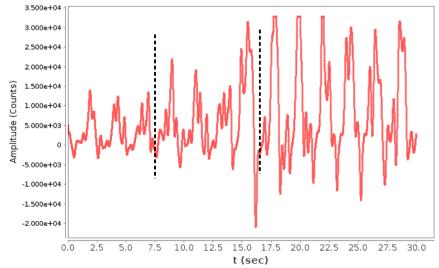

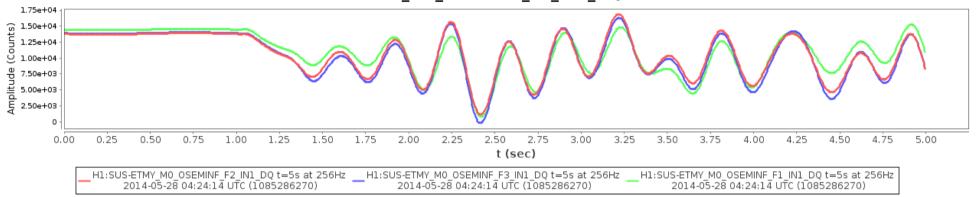

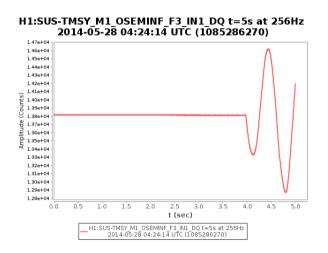

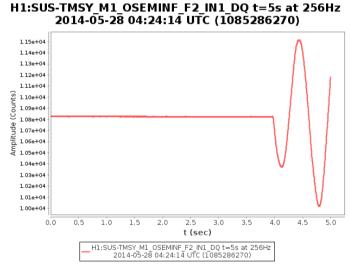

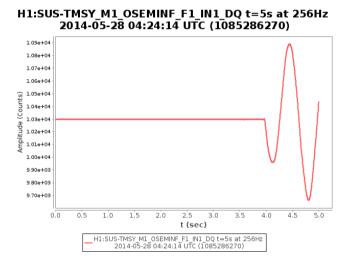

# $\begin{array}{c} \text{H1:SUS-ETMY\_M0\_OSEMINF\_F1\_IN1\_DQ, H1:SUS-ETMY\_M0\_OSEMINF\_F2\_IN1\_DQ, H1:SUS-ETMY\_M0\_OSEMINF\_F3\_IN1\_DQ} \\ \end{array}$

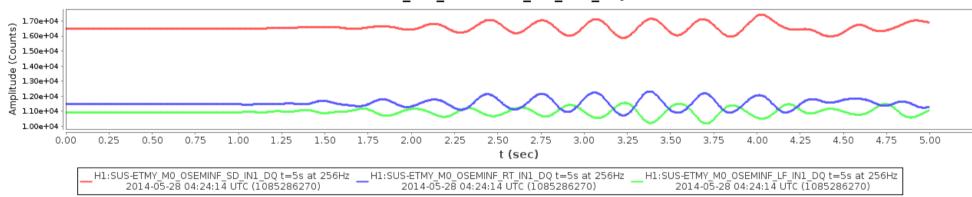

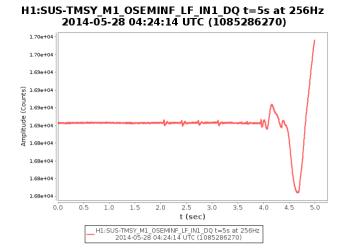

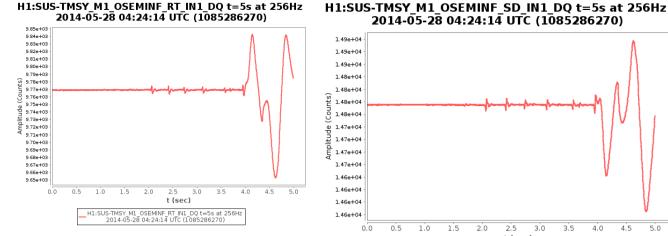

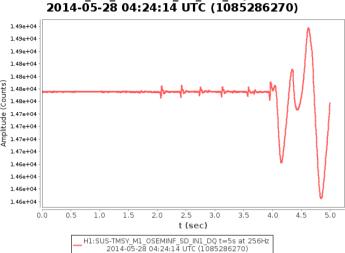

# $\begin{array}{c} \text{H1:SUS-ETMY\_M0\_OSEMINF\_LF\_IN1\_DQ, H1:SUS-ETMY\_M0\_OSEMINF\_RT\_IN1\_DQ, H1:SUS-ETMY\_M0\_OSEMINF\_SD\_IN1\_DQ} \end{array}$

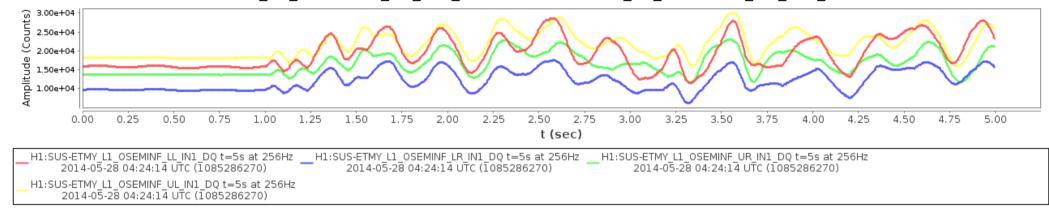

# H1:SUS-ETMY\_L1\_OSEMINF\_LL\_IN1\_DQ, H1:SUS-ETMY\_L1\_OSEMINF\_LR\_IN1\_DQ, H1:SUS-ETMY\_L1\_OSEMINF\_UR\_IN1\_DQ

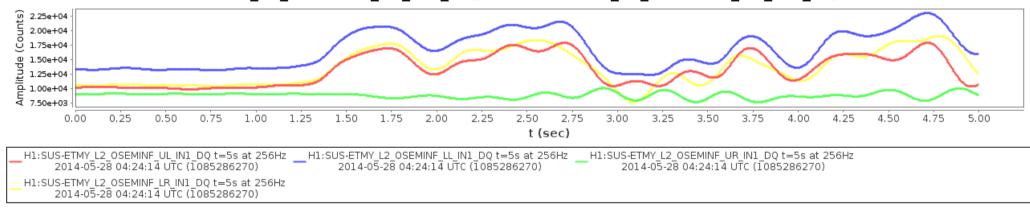

# H1:SUS-ETMY\_L2\_OSEMINF\_LL\_IN1\_DQ, H1:SUS-ETMY\_L2\_OSEMINF\_LR\_IN1\_DQ, H1:SUS-ETMY\_L2\_OSEMINF\_UR\_IN1\_DQ

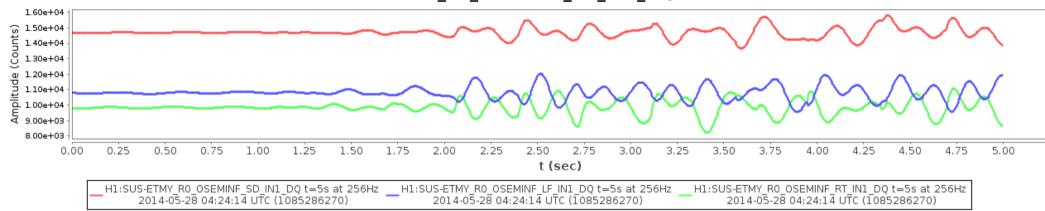

# H1:SUS-ETMY\_R0\_OSEMINF\_LF\_IN1\_DQ, H1:SUS-ETMY\_R0\_OSEMINF\_RT\_IN1\_DQ, H1:SUS-ETMY\_R0\_OSEMINF\_SD\_IN1\_DQ

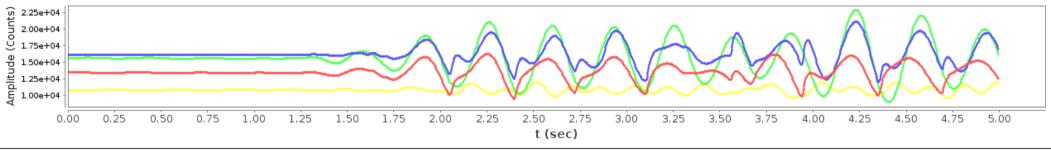

# H1:SUS-ETMY\_R0\_OSEMINF\_F1\_IN1\_DQ, H1:SUS-ETMY\_R0\_OSEMINF\_F2\_IN1\_DQ, H1:SUS-ETMY\_R0\_OSEMINF\_LF\_IN1\_DQ

2014-05-28 04:24:14 UTC (1085286270)

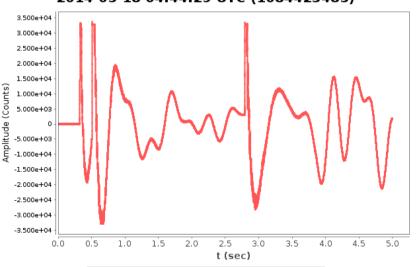

Shows up only on TMSY

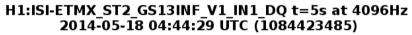

# H1:ISI-ETMY\_ST2\_GS13INF\_H3\_IN1\_DQ t=1s at 4096Hz 2014-05-28 04:24:16 UTC (1085286272)

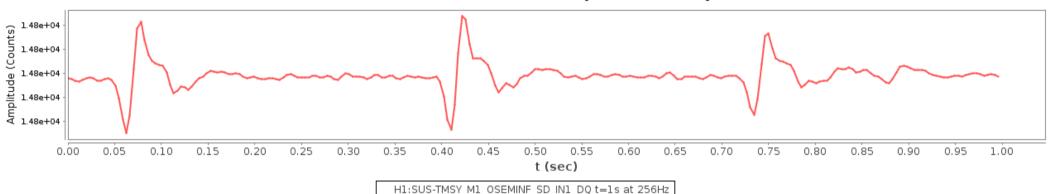

# H1:SUS-TMSY\_M1\_OSEMINF\_SD\_IN1\_DQ t=1s at 256Hz 2014-05-28 04:24:16 UTC (1085286272)

H1:SUS-TMSY\_M1\_OSEMINF\_SD\_IN1\_DQ t=1s at 256H 2014-05-28 04:24:16 UTC (1085286272)

\*\*\*\*

Need to investigate more on how the feedback signal is shut down

\*\*\*\*

Does TMSY hit a stop when the platform is shaken around? What can we do about it?