This is a follow up of 31765.

Sheila reported a very interesting behaviour in this past Wednesday (31765) and also the last Friday (31559) in which lowering the power recycling gain improved the sensitivity for some reason. This reminds us about the behaviour we encountered at 50 W in the past -- we spent a good amount of time trying to increase the power recycling gain, however, ending up with worse noise in the end. So I wanted to see if the behaviour Sheila saw was a same kind or not with a hope to get a hint for future improvement. I started looking at various power signals and etc, but no conclusion yet.

[Some observations]

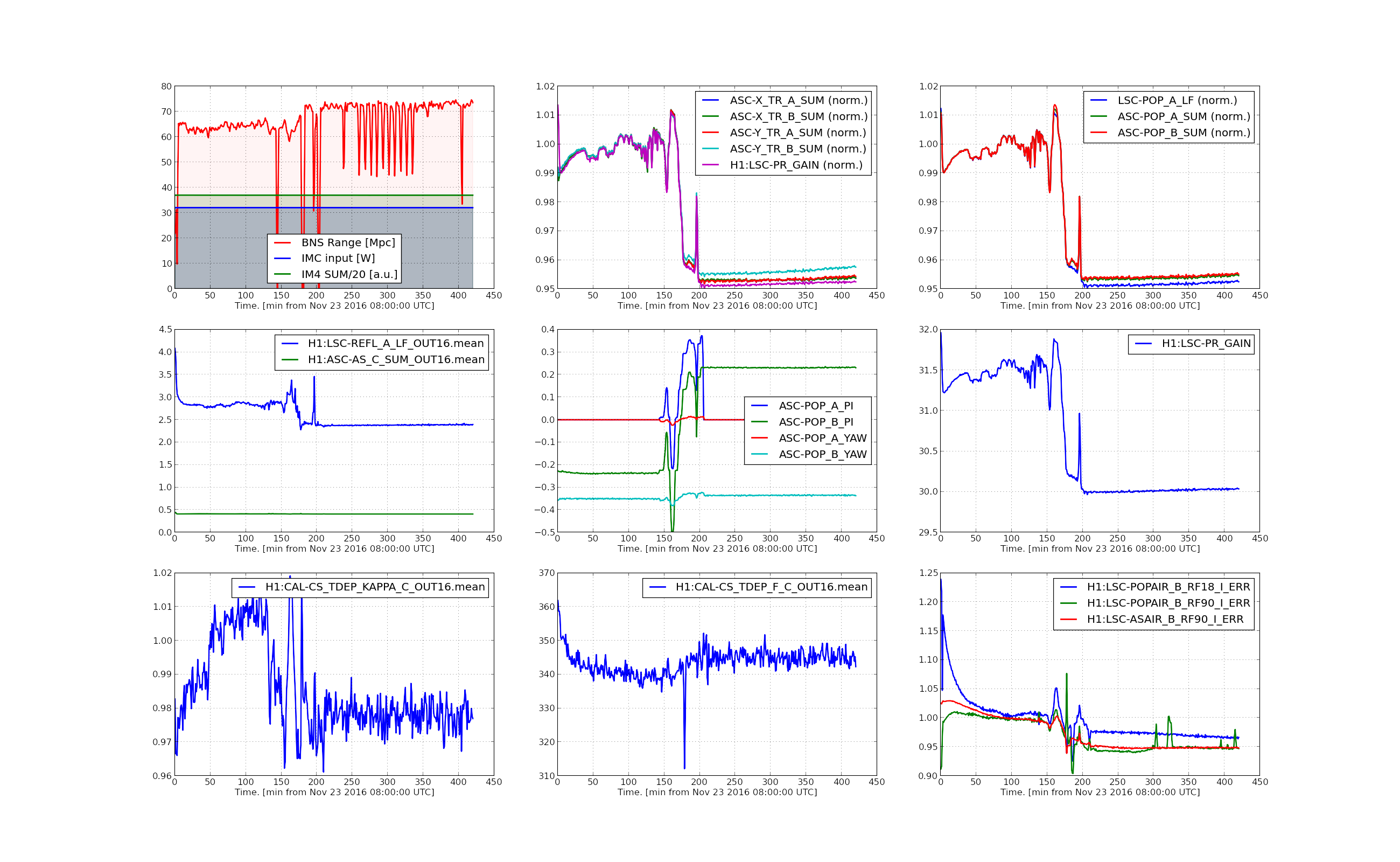

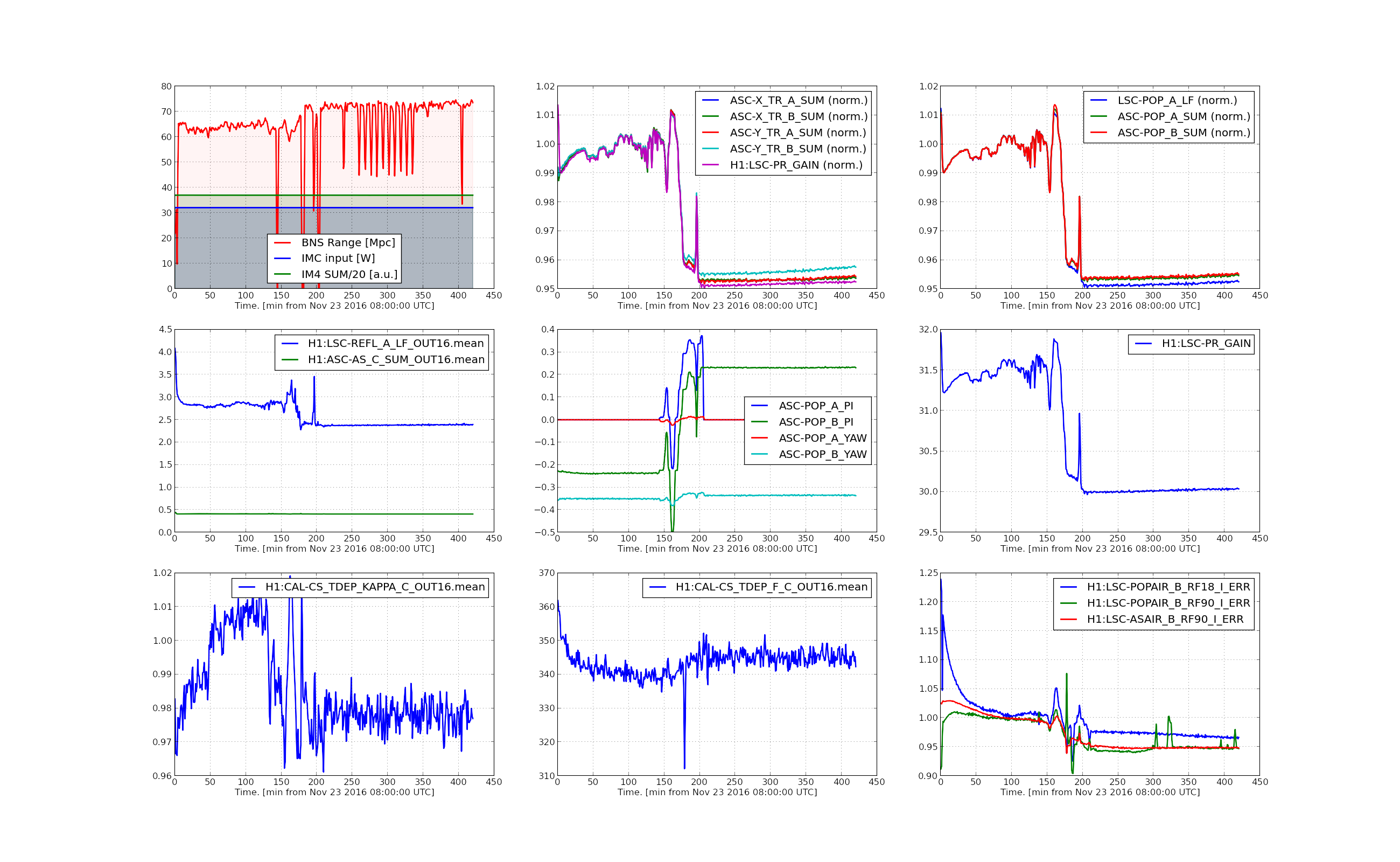

See the plot below.

This is a collection of some relevant signals for a lock stretch during of which Sheila was moving the PR3 spot position. In the middle plot in the 2nd row, POP_B_PIT shows the movement, changing its value from -0.2 to 0.2 counts. The upper left panel shows the improved BNS range coincided wit the PR3 move.

At the same time as the PR3 move, many power monitors dropped by almost 5% including, TR signals, POP powers. For the RF build ups, the 45 MHz sidebands seem to have dropped by the same amount of 5% by the PR3 movement, but the 9 MHz was affected a bit less. Another interesting thing is REFL LF, which decreased as the power recycling gain dropped, indicating that the interferometer approached closer to the critical coupling (assuming the mode matching stayed the same), or probably even passed the critical coupling as we have been having difficulty engaging the REFL WFSs (for example 31557).

Also, at the same time, the kappa_c value dropped by roughly 3% which is consistent with the decreased power recycling gain because the optical gain scales with the square root of the arm circulating power (when the DCPD's DC current was kept same). The cavity pole increased by 5Hz or so although I am not sure what this indicates in this case.

[Comparison with the 50 W case]

Looking at Stefan's plot in alog 28337, I see the typical behaviour that the 9 MHz sidebands drops a lot quicker than the recycling gains of the carrier and 45 MHz sidebands. This is due to the fact that the effective finesse for the 9 MHz is higher that the others, making the 9 MHz more vulnerable to losses. However, looking at the data from this past Wednesday, I found that the 9 MHz droped less steeper than the other two, see the lower right panel in the above plot. I don't know how this could happen in a smiple loss-increasing picture. Also, besides, the 9 MHz's initial drop (for 15 minutes or so at the very beginning) is smaller than the 50 W case presumably due to the less thermal lensing in the interferometer. It used to drop all the way to 40% of its maximum build up, while the recent drop goes to 75% of the maximum only.