J. Kissel, D. Barker, E. von Ries, R. McCarthy

We're trying to follow-up with LHO:77579, where it's reported that DuoTone signals are seen in the detector's sensitivity suring nominal low noise, as well as in the OMC DCPDs when there's no light on them (LHO:77696). In doing so, we're trying to decide which linear combinations of actions that LLO took with their IO chassis (see LHO:71308 and subsequent comments) are possible with LHO's segregated OMC DCPD IO chassis.

To investigate, in this aLOG, I quantify the voltage amplitude of the various signals in question in the current nominal configuration. LLO's measurement of the low-noise 524 kHz ADC with the AA chassis disconnected LHO:71190 indicates this is clearly an issue within the IO chassis, so we know we don't have to look at channels outside of there.

As such, I've looked at four relevant 524 kHz channels from H1's segregated OMC DCPD IO chassis:

- H1:OMC-DCPD_A0_IN1 :: One of the same DCPD channels that Joe looked at except at 524 kHz sample rate rather than 16 kHz, and either way, it's actually the sum of four of this low-noise 524 kHz ADC's channels, ADC0_0, ADC_0_4, ADC_8, and ADC_12

- H1:IOP-OMC0_MADC0_TP_CH0 :: The first channel on the low-noise 524 kHz ADC, containing the first copy of the OMC DCPD signal chain voltage.

- H1:IOP-OMC0_MADC0_TP_CH17 :: One of the four low-noise 524 kHz ADC channels I've shorted at the input to the AA chassis (see LHO:67465)

- H1:IOP-OMC0_ADC_DT_OUT :: the last ADC channel of this low-noise 524 kHz ADC (31st if you start counting at zero; 32nd if you start counting at one) which is a readback of the DuoTone timing signal itself

Unfortunately, exhaustive, fast studies are not possible because

(a) reading a 524 kHz channel requires 2 MB/sec of data, which is taxing on the RCG, so much so that one can only look at three 524 kHz channels at a time, and

(b) it's taxing on the data storage system, we we've only saved a bare minimum in the frames for all time. So, one has to make due with looking at these 524 kHz channels in real time, three at a time.

The calibration for these channels back into voltage is relatively simple, given that the low-noise 524 kHz ADC has 18 bits spread across the usual 40 [V] differential, peak to peak. The only trick is the OMC DCPD channel that one must divide by 4 again, because it's sum of four copies of the same voltage (see LHO:67439):

- H1:OMC-DCPD_A0_IN1 :: 40 [V_pp] / 2^18 [ct] * (1 / 4 [copies]) = 3.8147e-5 [V/ct]

- H1:IOP-OMC0_MADC0_TP_CH0 :: 40 [V_pp] / 2^18 [ct] = 1.5259e-4 [V/ct]

- H1:IOP-OMC0_MADC0_TP_CH17 :: 40 [V_pp] / 2^18 [ct] = 1.5259e-4 [V/ct]

- H1:IOP-OMC0_ADC_DT_OUT :: 40 [V_pp] / 2^18 [ct] = 1.5259e-4 [V/ct]

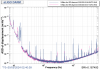

The first plot shows the time-series of the DuoTone readback channel (H1:IOP-OMC0_ADC_DT_OUT) in ndscope.

The amplitude of the DuoTone signal -- this beatnote between 960 and 961 Hz -- is 32000 [cts_pp], which is

32000 [ct_pp] * 1.5259e-4 [V/ct] = 4.8828 [V_pp]

= 4.8828 [V_pp] / (2*sqrt(2) [_pp / _rms])

= 1.723 [V_rms]

A 4.88 [V_pp] DuoTone signal seems quite unnecessarily loud, given that the noise floor of this low-noise 524 kHz ADC is 0.5e-6 [V_rms] = 0.5 [uV_rms] = 500 [nV_rms] in this frequency region.

Taking an ASD of the same DuoTone channel, the cumulative RMS at 955 Hz from the ASD is 1.2275 [V_rms], and we see lots of 1 Hz sidebands surrounding the excitation.

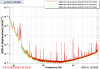

Taking an ASD of the shorted channel, the cumulative RMS at 955 Hz from the ASD is 2.10e-5 [V_rms], and it very coherent with the DuoTone channel at the DuotTone frequencies and their sidebands.

Taking an ASD of the OMC DCPDA (the average of CH0, CH4, CH8, CH12) and CH0 alone, with the DCPDs still connected to their entire signal chain, but there's no light on the DCPDs and I've turned the whitening switch OFF. In this configuration, I see a cumulative RMS at 955 Hz of 1.39e-4 [V_rms]. But the RMS is less interesting, because the RMS is not dominated by the DuoTone signal. However, we do see,

- OMC0_MADC0_TP_CH0 has comparable ASD of DuoTone lines as CH17, if not a bit louder, and

- OMC0_DCPD_A0_IN1 has *less* amplitude of DuoTone lines.

Quantitatively, the transfer function of MADC0_CH0 / DCPD_A0 at 960 Hz is 4.63 [V/V] and 961 Hz is 4.88 [V/V]. Very interesting / surprising that this transfer function ratio not exactly 4.0.

Next up == we're looking into various ways to turn OFF the timing signal temporarily to test how the timing signal is coupling into the ADC channels.

ASC-CHARD_Y couples in strongly at frequencies below 19Hz, which probably means we just need to tune the A2L gains again.

SUS-ITMY_L3 yaw couples in strongly below this frequency also.

ASC-OMC_A_YAW_OUT and ASC-OMC_QPD_A_YAW_OUT couples in strongly below 15 Hz and then again at around 26 Hz, which means there might be something coupling into the alginment of the beam into the OMC.

Worried about mutiple coherences with HEPI and PEM at around 27Hz also.