TITLE: Oct 6 DAY Shift 15:00-23:00UTC (08:00-04:00 PDT), all times posted in UTC

STATE Of H1: Commissioning

OUTGOING OPERATOR: Patrick

QUICK SUMMARY:IFO in commissioning mode as Maintenance Day begins.

TITLE: Oct 6 DAY Shift 15:00-23:00UTC (08:00-04:00 PDT), all times posted in UTC

STATE Of H1: Commissioning

OUTGOING OPERATOR: Patrick

QUICK SUMMARY:IFO in commissioning mode as Maintenance Day begins.

Expected Internet outage of about 15 minutes as one of our ISPs performs network maintenance this morning, between 0800 and 0900 Pacific (1500-1600 UTC).

TITLE: 10/06 [OWL Shift]: 07:00-15:00 UTC (00:00-08:00 PDT), all times posted in UTC STATE Of H1: Locked. Commissioning. SHIFT SUMMARY: Locked entire shift. One GRB alert. Went to commissioning at the end of the shift to allow Sheila to run injections. INCOMING OPERATOR: Ed ACTIVITY LOG: 11:08 - 11:18 UTC Stepped out of control room 14:18 UTC Went to commissioning to allow Sheila to run injections (WP 5528) 14:27 UTC Bubba driving to VPW 14:47 UTC Let Safety Clean truck through gate. Notified Bubba. SUS E_T_M_Y saturating (Tue Oct 6 11:22:48 UTC) SUS E_T_M_Y saturating (Tue Oct 6 13:54:13 UTC) From watching the monitor it seemed that RF45 coherence may have risen with the DARM spectrum during these saturations.

17:20 UTC Stopped/restarted gracedb query script 07:42 - 7:44 UTC Stepped out of control room 09:55 UTC GRB alert. Notified LLO. 10:30 - 10:36 UTC Stepped out of control room Still observing @ ~79 MPc.

I saw on a terminal on the ops workstation that someone had logged into h1fescript0 and started the query grace db script without running it in screen. I ctrl-c terminated that script. I did a listing of the current screen sessions (screen -ls) and saw two running. The one with PID 4403 had the printout from a crashed query db script. I restarted it in that screen and detached from the session. It is now running in screen with PID 4403.

TITLE: 10/06 [OWL Shift]: 07:00-15:00 UTC (00:00-08:00 PDT), all times posted in UTC STATE Of H1: Observing @ ~ 78 MPc. OUTGOING OPERATOR: Nutsinee QUICK SUMMARY: From the cameras the lights are off in the LVEA, PSL enclosure, end X, end Y and mid X. I can not tell if they are off at mid Y. Seismic in 0.03 - 0.1 Hz band is around .015 um/s. Seismic in 0.1 - 0.3 Hz band is around .1 um/s. Winds are less than ~5 mph.

TITLE: "10/05 [EVE Shift]: 23:00-07:00UTC (16:00-00:00 PDT), all times posted in UTC"

STATE Of H1: Observing at ~75 Mpc for the past 9 hours. Range recently went up to ~78 Mpc for no apparent reason.

SUPPORT: Mike

SHIFT SUMMARY: Quiet shift. Minimal/nominal seismic activity. Wind below 5mph. GraceDB querying failed once.

INCOMING OPERATOR: Patrick

ACTIVITY LOG:

23:51 Chris started HW injection.

01:41 Injection done

04:00 Noticed GraceDB querying failure. Restarted the python script. Called Mike about GraceDB events that weren't labeled as INJ.

I was following up the LHO loud glitches from 26th September. I had a look at the transmitted power signals as done in alog 20395 for dust glitches. The attached pdf contains the plots of band passed (10Hz-100Hz) DARM, as well as ASC-{X,Y}_TR_{A,B}_NSUM_OUT_DQ and SUS-ETMY_L3_MASTER_OUT_LL_DQ channels for the 8 time instances when ETMY saturation was observed. The ETMY saturation times are given below: 1127380417.6250 1127380418.6875 1127384361.3750 1127384361.8125 1127389556.1250 1127389556.2500 1127403691.3750 1127403691.5000 1127409078.3750 1127409078.5625 1127418386.1875 1127418386.4375 1127423722.0000 1127423722.1250 1127424221.7500 1127424222.0000 1127427748.9375 1127427749.0625 It can be noticed that the glitches also appear in Y TR signals (e.g., ASC-Y_TR_{A,B}_NSUM_OUT_DQ) with large amplitude except the 4th one. For the 4th glitch, it is not visible in ASC-Y_TR_{A,B}. In this particular case, , it is visible in X QPDs but much smaller than the other ones in Y. Also it doesn't look like that it is much above the noise in the QPD, and even the glitch shape in DARM seems different. In most of these cases DARM is going down and ASC-Y_TR_{A,B}_NSUM is going up initially. So it is interesting that in spite of ETMY saturation, the glitch shape is completely different as well as nothing can be found in Y QPDs.

Summary:

I performed 8 coherent H1L1 CBC hardware injections. They were all successful.

Waveforms:

Waveforms are in the hardware injection SVN: https://daqsvn.ligo-la.caltech.edu/svn/injection/hwinj/Details/Inspiral/${IFO}/coherentbbh*_1126259455_${IFO}.out

Waveform parameter files are in the hardware injection SVN: https://daqsvn.ligo-la.caltech.edu/svn/injection/hwinj/Details/Inspiral/coherentbbh*_1126259455.xml

Schedule:

The following was appended to the schedule:

1128124325 1 1.0 coherentbbh1_1126259455_

1128125225 1 1.0 coherentbbh2_1126259455_

1128126125 1 1.0 coherentbbh3_1126259455_

1128127025 1 1.0 coherentbbh4_1126259455_

1128127925 1 1.0 coherentbbh5_1126259455_

1128128825 1 1.0 coherentbbh7_1126259455_

1128129725 1 1.0 coherentbbh8_1126259455_

1128130625 1 1.0 coherentbbh9_1126259455_

Recall we had the issue before where injections were being cancelled since they triggered an EM alert for testing. Peter S. documented what needed to be changed in aLog 22163. I reset ${IFO}:INJ-CAL_TINJ_PAUSE and ${IFO}:INJ-CAL_EXTTRIG_ALERT_TIME between injections so that they were not cancelled. It worked.

The gracedb entries for these injections are H190051 to H190068.

I've attached omegascans of the injections.

Since the current set of hardware injections is testing the injections themselves, not the human response to event candidates, I have changed the Approval Processor configuration to no longer treat hardware injections like real GW event candidates. That means that they will not get the H1OPS and L1OPS labels, and operators will not be presented with a sign-off box for them. However, with the CURRENT version of the external alert code (ext_alert.py), audible alerts will still sound in the control rooms. I am trying to arrange that during tomorrow's maintenance period we will update the ext_alert.py scripts so that the audible alerts sound only for triggers that operators are asked to sign-off on. After that change is made (hopefully tomorrow), please take any audible alert seriously as a genuine external-trigger alert or low-latency GW trigger alert. Exception: we are planning to set up weekly tests of the alert system that will happen during Tuesday maintenance periods; details to come later.

O1 days 16,17

Saturday 3rd October 2015. Many unexpected restarts of h1fw0 due to failed SSD raid. No other restarts reported. Details in attached text file.

Sunday 4th October 2015. Many unexpected restarts of h1fw0 due to failed SSD raid. No other restarts reported. Details in attached text file.

TITLE: 10/5 [EVE Shift]: 23:00-07:00UTC (16:00-00:00 PDT), all times posted in UTC"

STATE Of H1: Observing at ~74 Mpc for the past 2.5 hours

OUTGOING OPERATOR: Corey

QUICK SUMMARY: Chris Biwer have just started Burst HW injection at 23:55. This will continue for the next two hours. No seismic activity in the earthquake band. Wind below 5mph.

I am starting some coherent H1L1 hardware injections test. There will be the 8 test injections that Adam and I did not get a chance to perform last Friday. I will add a comment with the schedule when it they have been added. More details to follow later.

The schedule was appended with: 1128124325 1 1.0 coherentbbh1_1126259455_ 1128125225 1 1.0 coherentbbh2_1126259455_ 1128126125 1 1.0 coherentbbh3_1126259455_ 1128127025 1 1.0 coherentbbh4_1126259455_ 1128127925 1 1.0 coherentbbh5_1126259455_ 1128128825 1 1.0 coherentbbh7_1126259455_ 1128129725 1 1.0 coherentbbh8_1126259455_ 1128130625 1 1.0 coherentbbh9_1126259455_

Last scheduled injection performed. More details later.

TITLE: 10/5 DAY Shift: 15:00-23:00UTC (08:00-16:00PDT), all times posted in UTC

STATE of H1: Observation Mode at 78Mpc

Incoming Operator: Nutsinee

Support: Full Room

Quick Summary:

~46hr Lock ended by 6.0 Chilean EQ noted by Terramon. Then went through some acquisition exercises while we waited for the seismic to die down. H1 brought back to Observation Mode in the afternoon and it is humming along swimingly.

Shift Activities:

I have spent some time trying to understand the behavior of the CARM loop in full lock.

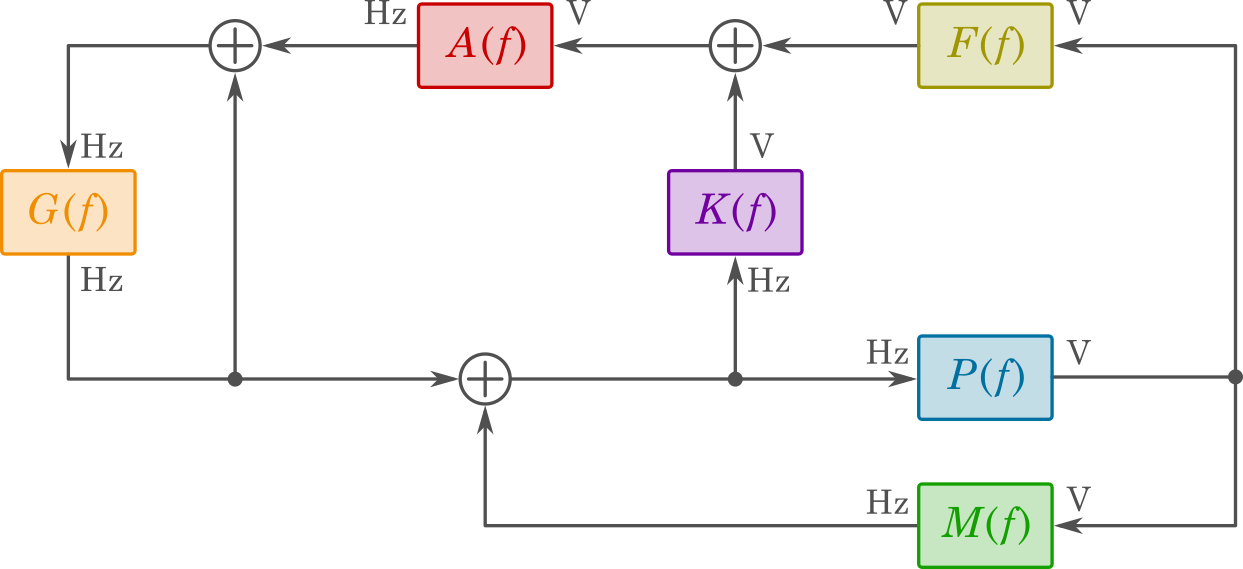

First, I have reduced the loop to the following block diagram:

P is the IFO, K is the IMC, and G is the FSS. F and M represent the fast and slow common-mode feedback paths, and A represents the IMC PDH board and the VCO. A fuller accounting of these blocks is given in the sections below.

The OLTF of CARM is then given by

where is the CLTF of the FSS. For the time being, I have ignored the slow IMC feedback (the crossover with the fast path happens below 100 Hz) and I have assumed the CLTF of the FSS is −1.

The model (described below) shows OK agreement with the measurement (taken 2015-08-14) between 1 and 40 kHz, but above that there is significant deviation in the phase.

I have also included a plot of the modeled IMC OLTF . Getting the model to agree with the measurement requires the inclusion of a mystery gain of 1/3, which I have rolled into the optical plant. Previous measurement of the IMC modulation index provided only an upper limit (which I have used here), so I am hoping that this explains some of the mystery gain.

The CARM plant is the TF taking laser frequency fluctuation to rf power on REFL9Q. It consists of the following (at 24 W):

This is multiplied by the PD TF, the SNB TF, and the CMB common TF:

Note that since this measurement we've added 7 dB to the common gain, and correspondingly removed 7 dB from the fast and slow paths. But that shouldn't matter for the OLTF estimate.

Not yet implemented. So far I have only considered the portion of the loop for which |AF| ≫ |M|.

IMC optical plant, 24 W:

PD response 880 V/W [responsivity 0.37 A/W (LHO#5277), transimpedance 476 V/A (ibid.), demod TF 5 V/V (rf volts to if volts; D0902745)]

IMC REFL input gain −3 dB [nominally 17 dB at 2.5 W PSL power]

Currently, the CLTF G/(1 − G) is assumed to be −1. I have a measurement of G from Peter K, but I have not yet included it here. Below 100 kHz, the CLTF deviates from −1 Hz/Hz by less than 50 % in magnitude and 5° in phase (see attachment).

IMC common/fast path TF:

IMC VCO TF:

Evan has told me that the above diagram and OLTF equation are wrong.

He's given me the liberty to preempt the publication of his thesis and provide the erratum for this entry.

The open loop gain transfer function of the CARM loop is defined by the attached diagram,

H = bar{G} A K P (F/K + M) / (1 - bar{G} A K)

Where again,

G = open loop gain of the FSS

bar{G} = G / (1-G) = closed loop gain TF of the FSS

A = the IMC Common Mode Board and IMC VCO

P = electro-optical CARM plant of the IFO

K = electro-optical IMC plant

F = CARM fast path through CARM Common Mode Board (fed to the input of the IMC Common Mode Board to IMC VCO)

M = CARM slow path to IMC Length control of MC2

Sorry, had a busy morning/afternoon.

Had a 6.0 EQ from Chile knock us out of lock (17:21). Seismic signals were elevated for about an hour, so waited that out. Then after that I did a few tweaks to see if we could reacquire with the alignment we had been running. Gave H1 about an hour while we waited. Then we called that off, and went for an Initial Alignment. H1 then locked up with mostly no issues shortly thereafter.

The minor issues we did have were related to making some Guardian changes ("we" being Sheila) to include PRMI into lock acquisition. I believe she also added an OMC PZT slider step as well.

Once at NOMINAL_LOW_NOISE, Sheila took some time to run some commissioning work while L1 was down.

21:35 Went back to Observation (@73Mpc)

Just to clarify, we noticed a problem with the PRMI state that has been in place (It did not turn off the offloading to PRM top mass if it failed to make the transition to DRMI). I made some changes to fix this, which created a different problem. Now I think it should be fixed, but we haven't fully tested it. I hope to test the fix fully durring maintence tomorow, but for tonight if anyone decides to use these and runs into a problem feel free to give me a call.

I didn't do the OMC thing yet, that will be done durring maintence tomorow.

Also:

We were locked for a little bit before LLO rocovered from the EQ, so I had a chance to make a quick injection on ITMX ISI ST2 in the X direction (WP#5528). I used 0.0283 cnts at 75 Hz starting at 21:18 UTC October 5. The result is that it seems like if the 77-80 Hz noise is from scattered light, the scattering path does not include anything hanging off the ITMX ISI. With the same excitation applied to the ETMX ISI we had a borad peak in DARM, with this excitation on the ITM ISI we get a narrow peak which is a factor of 10 lower.